# A. A. Prihozhy

# ANALYSIS, TRANSFORMATION AND OPTIMIZATION FOR HIGH PERFORMANCE PARALLEL COMPUTING

Minsk BNTU 2019 **Prihozhy**, **A. A.** Analysis, transformation and optimization for high perfomance parallel computing / A. A. Prihozhy. – Minsk: BNTU, 2019. – 229 p. – ISBN 978-985-583-366-7.

This book studies hardware and software specifications at algorithmic level from the point of measuring and extracting the potential parallelism hidden in them. It investigates the possibilities of using this parallelism for the synthesis and optimization of high-performance software and hardware implementations. The basic single-block flow model is a result of the algorithm transformation, and is a basis for developing efficient methods of synthesis and optimization of parallel implementations. It supports the generation and optimization of computational pipelines and concurrent net algorithms, which lead to higher performances of the computing systems.

This book is useful in training of scientific researchers and graduate students. It is also useful for teaching students and undergraduates in computer science at universities.

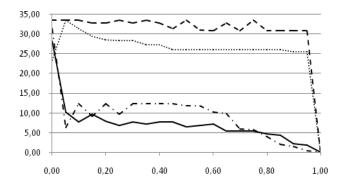

Tables 34. Figures 117. Bibliography 91.

Recommended for publication by the Scientific and Technical Council of Belarusian national technical university (Record № 1, 18.01.2019)

#### Reviewers:

Head of the Department of information management systems, Belarusian national university, Dr. Prof. V. V. Krasnoproshin; Professor of the Info-communication technologies department, Belarusian university of informatics and radio-electronics, Dr. Prof. A. A. Boriskevich

# **CONTENT**

| PREFACE                                                                                                      | 9          |

|--------------------------------------------------------------------------------------------------------------|------------|

| INTRODUCTION                                                                                                 | 10         |

| Chapter 1. EVALUATION OF COMPUTATIONAL COMPLEXITY, CRITICAL PATH AND PARALLELIZATION POTENTIAL OF ALGORITHMS | 13         |

| 1.1. Metrics of algorithms                                                                                   | 13         |

| 1.1.1. Computational complexity of algorithm                                                                 | 13         |

| 1.1.2. Critical path analysis problem                                                                        | 14         |

| 1.1.3. Parallelization potential of algorithm                                                                | 17         |

| 1.2. Methodology of algorithm critical path evaluation                                                       | 17         |

| 1.2.1. Data Flow Execution Graph                                                                             | 19         |

| 1.2.2. Computational complexity of data flow execution graph.                                                | 20         |

| 1.2.3. Critical path on data flow execution graph                                                            | 23         |

| 1.2.4. Parallelization potential and feasible acceleration                                                   | 25         |

| 1.3. Evaluation of computational complexity and critical path on data flow execution graph                   | 26         |

| 1.3.1. Explicit evaluation of critical path                                                                  | 26         |

| 1.3.2. Dynamic evaluation of critical path                                                                   | 28         |

| 1.4. Tool for estimation of algorithm parallelization potential                                              | 28         |

| 1.4.1. Instrumenting and mapping C-code onto C++-code                                                        | 28         |

| 1.5. Reduction of critical path and increase of parallelism                                                  | 34         |

| 1.5.1. Reduction by transformation of C/C++-code                                                             | 34         |

| 1.5.2. Preliminary transformation of loops                                                                   | 37         |

| 1.5.3. Extraction of computations from control structures                                                    | <i>3</i> 8 |

| 1.5.4. Transformation of expressions                                                | 40  |

|-------------------------------------------------------------------------------------|-----|

| 1.5.5. Effectiveness of transformations                                             | 41  |

| 1.6. Evaluation accuracy and limitations.                                           | 43  |

| 1.7. Conclusion.                                                                    | 44  |

| Chapter 2. PARALLELIZATION POTENTIAL OF MEANINGFUL HARDWARE / SOFTWARE APPLICATIONS | 45  |

| 2.1. Parallelization potential of two-dimensional WAVELET codec                     | 45  |

| 2.2. Parallelization potential of RSAREF cryptographic toolkit                      | 49  |

| 2.3. Parallelization potential of MPEG-4 video codec                                | 51  |

| 2.3.1. MPEG-4 video codec                                                           | 51  |

| 2.3.2. Source video sequence                                                        | 55  |

| 2.3.3. Profiling computational complexity                                           | 55  |

| 2.3.4. Profiling critical path                                                      | 57  |

| 2.3.5. Profiling parallelization potential                                          | 61  |

| 2.4. Conclusion                                                                     | 66  |

| Chapter 3. TRANSFORMATION OF ALGORITHM TO BASIC SINGLE-BLOCK MODEL                  | 67  |

| 3.1. Algorithm transformation flow                                                  | 67  |

| 3.2. Preliminary transformation of algorithm                                        | 71  |

| 3.3. Basic single-block flow model                                                  | 74  |

| 3.4. Transformation of loops for basic single-block model                           | 79  |

| 3.5. Transformation of nested branching code to basic single-block model            | 85  |

| 3.6. Efficiency of basic single-block model                                         | 90  |

| 3.7. Conclusion                                                                     | 100 |

| Chapter 4. ANALYSIS OF BASIC SINGLE-BLOCK MODEL 102                        |

|----------------------------------------------------------------------------|

| 4.1. Goals of analysis                                                     |

| 4.2. Analysis of structured basic single-block model102                    |

| 4.2.1. Evaluating conditional variables using Boolean expressions103       |

| 4.2.2. Relations among values of primary Boolean variables 105             |

| 4.2.3. Pairs of orthogonal conditional variables106                        |

| 4.2.4. Estimating metrics of basic single-block model108                   |

| 4.3. Advanced analysis of basic single-block model111                      |

| 4.3.1. Feasibility functions for pairs of primary Boolean variables112     |

| 4.3.2. Feasibility functions and pairs of orthogonal variables 115         |

| 4.4. Formal method of basic single-block model analysis118                 |

| 4.4.1. Tautology problem for a pair of conditional variables 118           |

| 4.4.2. Partial tautology problem for orthogonal variables 118              |

| 4.4.3. Contradiction procedure and SAT problem for orthogonal variables119 |

| 4.4.4. Problem solving over minimization of partial functions 120          |

| 4.4.5. Orthogonal subsets of the set of conditional variables 122          |

| 4.5. Analysis of basic single-block model with control flow feedback122    |

| 4.6. Conclusion                                                            |

| Chapter 5. SYNTHESIS AND OPTIMIZATION OF COMPUTATIONAL PIPELINES           |

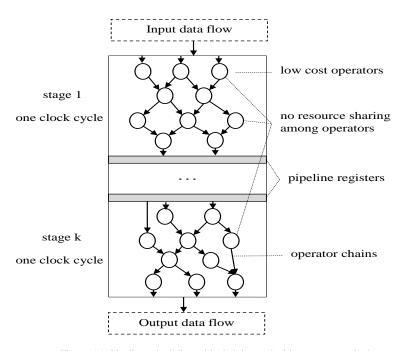

| 5.1. Computational pipelines129                                            |

| 5.2. Pipelining of algorithms130                                           |

| 5.3. Pipelining data flow programs                                         |

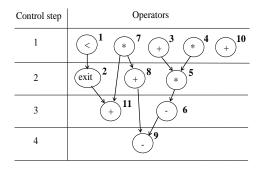

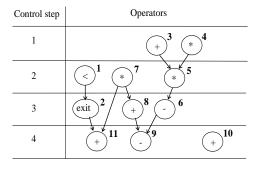

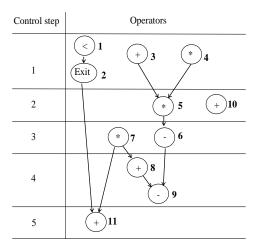

| 5.4. Modeling pipelines with relations and graphs                                         | 134     |

|-------------------------------------------------------------------------------------------|---------|

| 5.4.1. Relations and graphs on sets of operators, variables and pipeline-stages           | 134     |

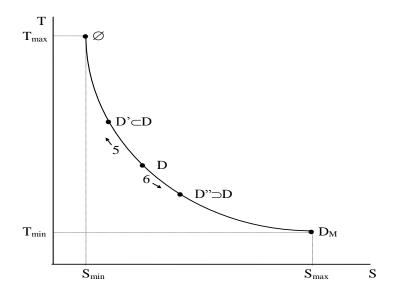

| 5.4.2. Number of pipeline stages versus stage time                                        | 139     |

| 5.4.3. As soon as possible (ASAP) and as late as possible (ALAP) pipeline schedules       | 140     |

| 5.5. Time constrained optimization of pipelines                                           | 140     |

| 5.5.1. A set of pipelines with the same stage time                                        | 140     |

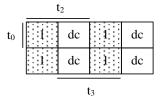

| 5.5.2. Evaluation of overall pipeline registers size                                      | 142     |

| 5.5.3. Optimization task: objective function and constraints                              | 143     |

| 5.6. Least cost search branch and bound technique for pipeline optimization               |         |

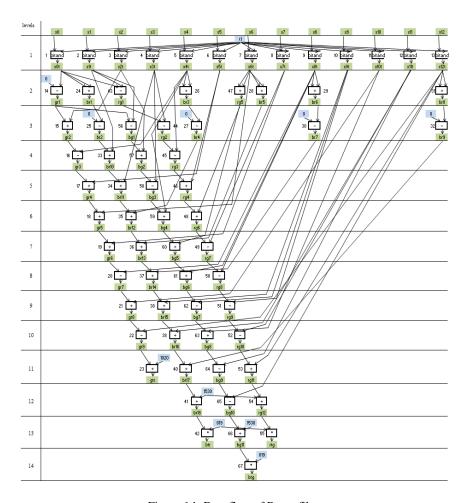

| 5.6.1. Pipeline schedule search tree                                                      | 144     |

| 5.6.2. Incomplete mapping of operators onto pipeline stages.                              | 146     |

| 5.6.3. Updating overall registers size lower bound                                        | 146     |

| 5.6.4. Computing earliest and latest pipeline stages of operate                           | tor 148 |

| 5.6.5. Operators assignment conflict                                                      | 149     |

| 5.6.6. Least cost search branch and bound minimization of overall pipeline registers size | 149     |

| 5.7. Heuristic technique for optimization of pipelines                                    | 151     |

| 5.7.1. Dynamic evaluation of earliest and latest stages of operator                       | 152     |

| 5.7.2. Dynamic estimation of overall registers size lower bound                           | 153     |

| 5.7.3. Dynamic ordering of operators                                                      | 154     |

| 5.7.4. Heuristic technique for pipeline optimization                                      | 157     |

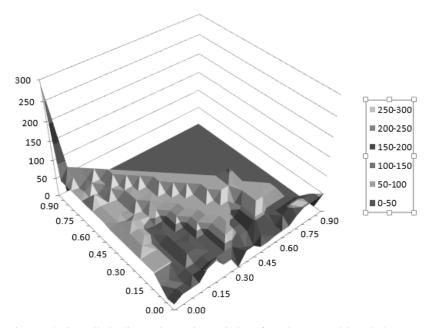

| 5.7.5. Tuning heuristic factors                                                           | 158     |

| 5.8. Conclusion                                                              |

|------------------------------------------------------------------------------|

| Chapter 6. OPTIMIZATION OF PIPELINES FOR REMARCABLE APPLICATIONS160          |

| 6.1. Bayer filter based on improved linear interpolation                     |

| 6.2. Forward 8×8 discrete cosine transform164                                |

| 6.3. Experimental results for random middle size designs                     |

| 6.4. Experimental results for random large size designs168                   |

| 6.5. Conclusion                                                              |

| Chapter 7. GENETIC ALGORITHM FOR TUNING OPTIMIZATION HEURISTICS170           |

| 7.1. Heuristics for solving optimization problems170                         |

| 7.2. Motivation of tuning heuristics172                                      |

| 7.3. Genetic algorithm of tuning heuristics174                               |

| 7.3.1. Basics                                                                |

| 7.3.2. Genetic operations174                                                 |

| 7.3.3. Genetic algorithm178                                                  |

| 7.4. Two modes of exploiting the genetic algorithm179                        |

| 7.4.1. Solving optimization problem179                                       |

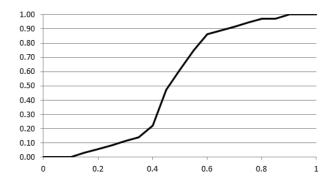

| 7.4.2. Evaluation of cumulative distribution functions                       |

| 7.4.3. Evaluation of cumulative distribution functions                       |

| 7.5. Experimental results                                                    |

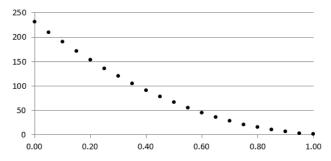

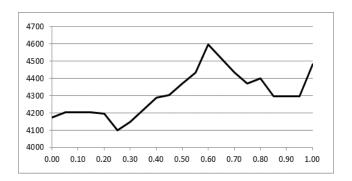

| 7.5.1. Test benches for pipeline optimization181                             |

| 7.5.2. Optimization of heuristics182                                         |

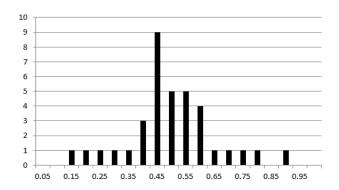

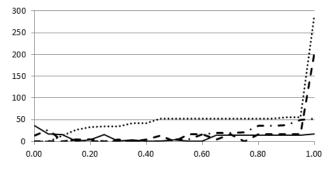

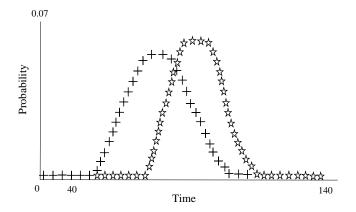

| 7.5.3. Cumulative distribution probability functions of heuristic factors185 |

| 7.5.4. Tuning genetic algorithm                                                           | 186 |

|-------------------------------------------------------------------------------------------|-----|

| 7.5.5. Effectiveness of genetic algorithm                                                 | 187 |

| 7.6. Conclusion                                                                           | 188 |

| Chapter 8. NET ALGORITHMS                                                                 | 189 |

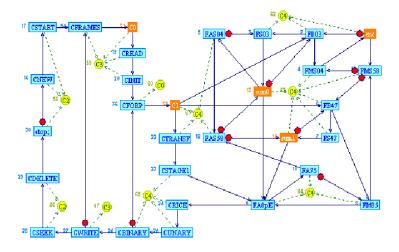

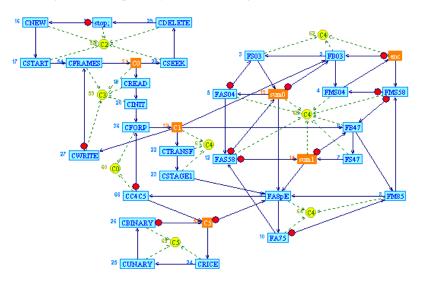

| 8.1. Sequential scheduling of algorithms                                                  | 189 |

| 8.2. Net scheduling of algorithms                                                         | 193 |

| 8.2.1. Net schedule                                                                       | 193 |

| 8.2.2. Optimizing a net schedule                                                          | 196 |

| 8.2.3. Tackling the existence problem                                                     | 201 |

| 8.3. Generating a net schedule                                                            | 206 |

| 8.4. Transition from net schedule to sequential schedule                                  | 208 |

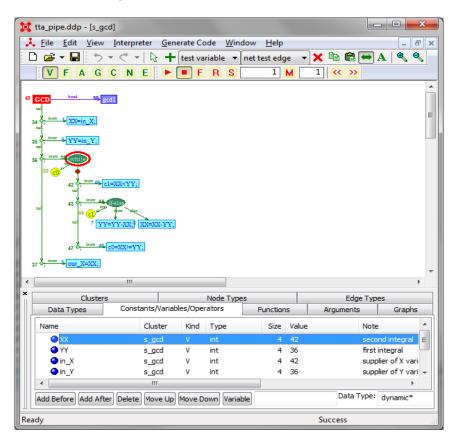

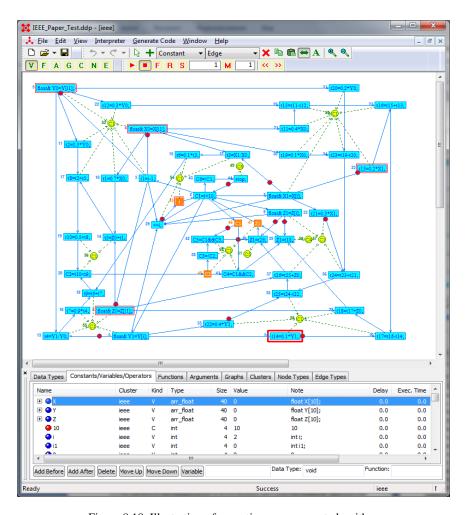

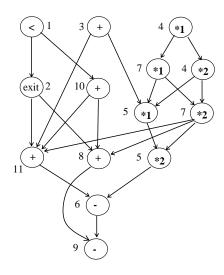

| 8.5. Graph language and tool for creation and simulation of sequential and net algorithms | 209 |

| 8.6. Experimental results                                                                 | 215 |

| 8.7. Conclusion                                                                           | 219 |

| REFERENCES                                                                                | 220 |

#### **PREFACE**

An algorithmic description of a solution of an applied, scientific or technical problem is given, for which it is necessary to obtain a highperformance software implementation on a multiprocessor or multi-core system, or a hardware implementation on an FPGA or ASIC. How to perform the mapping of the source algorithm onto an efficient parallel implementation? How to discover, measure, extract and optimally implement the hidden parallelism is the main objective of this book. This book develops a technology for analyzing, transforming, optimizing and mapping hard-to-parallel algorithms and programs to pipeline and network implementations. The algorithm analysis is based on the profiling of the program in order to measure the computational complexity, the critical path and the potential parallelism on realistic input data. The transformation performs parallelism extraction from the program, preserving the original functionality. The synthesis and optimization improves the structure and parameters of computational pipelines and network computing schedules.

This book will be useful for scientific researchers, engineers, PhD students and undergraduates. It is mostly based on author's publications written during more than 25 years period and presents state of the art in scientific direction under consideration. The author's works have been published by such well known publishers as IEEE, Kluwer Academic Publishers, Springer and many others.

My gratitude is large to my partners and friends Dr. Jean Mermet and Dr. Bernard Courtois (France), as well as to Dr. Marco Mattavelli, Dr. Daniel Mlynek, Dr. Alain Vachoux, Dr. Masimo Ravasi, Dr. Ab Al Hadi Bin Ab Rahman, Dr. Simone Casale-Brunet and Dr. Endri Bezati (Switzerland) for collaboration, joint work and joint publications.

The author acknowledges the colleagues of computer and system software department, the colleagues of the faculty of information technologies and robotics, and the scientific research sector of the Belarusian National Technical University, who have helped in preparing the manuscript and in getting approval to publish this book.

Anatoly Prihozhy Minsk, December, 2018 prihozhy@yahoo.com

#### INTRODUCTION

This book has a coherent logical thread, revealing the topic stated in the title. It outlines the models and methods of analysis, transformation and optimization of algorithms and programs for effective highperformance parallel execution on multiprocessor systems.

Firstly, we explore the metrics of algorithms and programs, providing the estimation of the hidden, but potentially retrievable and implementable dataflow parallelism. We consider three metrics, namely, computational complexity, critical path and the parallelization factor on the graph of program execution. This graph is formed dynamically during the execution of the program code on specific source data. These data reflect the most realistic conditions for the application of the algorithm, and not the conditions of the "worst case", which is crucial for an objective and reliable assessment. In order to measure the values of metrics, we develop a model and method for instrumenting and extending the program code of an algorithm, create appropriate tools, and perform measurements on a number of important algorithms for processing video and audio information, as well as on cryptographic algorithms.

After the potential parallelism has been measured, and the expediency of paralleling the algorithm is justified, the program code transformation stage begins in order to extract the data flow. This book describes a set of rules for the transformation of various kinds of statements, control structures of the programming language and super positions of them, to the basic single-block flow model that is built on a single loop. One part of the control instructions is deleted, the other part is split. As a result, the data flow becomes extremely dominant in the presentation of algorithm. The proposed method provides the extraction of a dataflow from difficultly parallelizable algorithms.

The basic single-block flow model makes operators less dependent on one another and freer with respect to the permutation. However, it makes it difficult to analyze the transformed code with respect to identifying mutually exclusive branches, compared to the source code. The analysis method proposed in the book uses the theory of Boolean functions and formal logic. The search for mutually exclusive operators that are under conditional if-then instructions is equivalent to checking the orthogonality of Boolean conditional variables, which in turn is equivalent to

checking the tautology of Boolean expressions. Analysis of algorithms with feedback in the control flow due to presence of loop statements is performed by the method of mathematical induction.

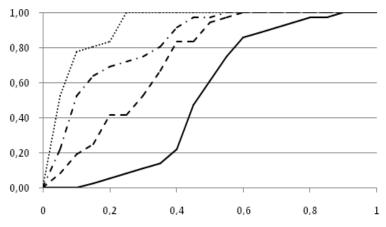

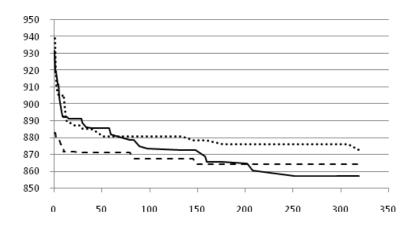

The basic single-block flow model of an algorithm is an efficient source of synthesis and optimization of computational pipelines. It is a source of generating a series of relations and graphs on sets of operators and variables. The graph of operator conflicts that arise when operators are assigned to pipeline stages, allows us to solve the problem of minimizing the number of stages for a given constraint on the operation time of one pipeline stage. Another important parameter is the size of the buffers used to push data through the pipeline. The total size of the buffers should be minimized. Two algorithms optimize the pipeline: accurate and heuristic. The exact algorithm is capable of finding the global optimum for a small-size pipeline. The heuristic algorithm is capable of finding a near-optimal solution for a large-size pipeline. The developed software has allowed to synthesize and optimize pipelines used in practically significant applied areas. Experiments performed on large algorithmic descriptions taken from real practice and generated by random number generators showed that the proposed heuristic pipeline optimization algorithm yields significantly better results than such algorithms like ASAP and ALAP.

The quality of the optimization results obtained by the heuristic algorithm substantially depends on the composition of the heuristics and the weight of each of them in the integrated heuristic, which is used to select the preferred solution when searching for the optimal parallel implementation of the algorithm. The problem of setting up heuristics for a specific paralleling problem and a specific paralleling algorithm is solved in this book by using a genetic algorithm. We construct chromosomes, a fitness function, a generation and population of chromosomes, selection, and crossover and mutation genetic operations over chromosomes to determine the significance of each heuristic in the paralleling algorithm. The use of the genetic algorithm is illustrated by the example of a heuristic algorithm for optimizing computational pipelines. Experiments have shown that the genetic algorithm can significantly improve the quality of synthesized pipelines.

The basic single-block flow model of the algorithm is a source of synthesis and optimization of network computing schedules and network algorithms. We give a definition of a network schedule, describes a method of estimating the execution time and implementation cost of the schedule over the cliques of the graph of sequential execution of operators and over the cliques of the graph of parallel execution of operators. Further, we formulates and solve the problem of the existence of a network schedule for a given level of parallelism. The schedule is optimized on the minimum of execution time, or on the minimum of consumed computing resources. The book describes an instrumental system that supports a graphs-description language, allows to interactively create network algorithm graph-descriptions, performs the simulation of the graph-descriptions, and optimizes the network schedules.

All models and methods of analysis, transformation and optimization of algorithms for parallel efficient execution are illustrated with a number of examples. The developed software tools are applied to several practically significant hardware and software applications. In particular, they are applied to two-dimensional WAVELET codec, RSAREF cryptographic toolkit, MPEG-4 video codec, Bayer filter, 8×8FDCT, and middle-size and large-size random designs.

## 1. EVALUATION OF COMPUTATIONAL COMPLEXITY, CRITICAL PATH AND PARALLELIZATION POTENTIAL OF ALGORITHMS

#### 1.1. Metrics of algorithms

This chapter presents metrics for evaluating the computational complexity, critical path and parallelization potential of algorithms that are represented and executed as a computer program. The model metrics aim at the estimation and increase of the upper bound of the algorithm execution speed on a parallel computing platform. They are particularly tailored for application to network, multimedia, cryptographic, scientific and other complex algorithms.

#### 1.1.1. Computational complexity of algorithm

The computational complexity theory [31] classifies computational problems according to their difficulty, and relating the complexity classes to each other. A computational problem is understood to be a task that is in principle amenable to being solved by an algorithm, and therefore may be solved by a computer. The theory introduces mathematical models of computation to study the computational problems and quantifying their computational complexity, i.e., the amount of resources needed to solve them, such as time and storage.

The analysis of computational complexity of an algorithm aims at analyzing the amount of resources needed by a particular algorithm. Usually, this involves determining a function that relates the length of an algorithm's input to the number of steps the algorithm takes, or the number of storage locations it uses. An algorithm is said to be efficient when this function's values grow slowly compared to a growth in the size of the input. Different inputs of the same length may cause the algorithm to have different behavior. Best, worst and average case trends are often of practical interest. The function describing the performance of an algorithm is usually an upper bound, which is determined from the worst case inputs to the algorithm.

The term *analysis of algorithms* was introduced by Donald Knuth [32-34]. Algorithm analysis provides theoretical estimates for the re-

sources needed by any algorithm which solves a given computational problem. These estimates provide an insight into reasonable directions of search for efficient algorithms.

The theoretical analysis of algorithms determines the complexity function for arbitrarily large input, and uses big O notation (big-omega notation) and Big-theta notation. Asymptotic estimates are preferable because different implementations of the same algorithm may differ in efficiency. Exact (not asymptotic) measures of efficiency can sometimes be computed but they usually require certain assumptions concerning the particular implementation of the algorithm, called model of computation.

Nowadays, processing and compression algorithms, communication protocols and multimedia systems have reached an extremely high level of sophistication. Architectural implementation choices based on designer feeling or intuition without objective measures and verifications become extremely difficult or impossible tasks.

The increasing complexity of the algorithms has lead to the need of specifications and more intensive validations of such system descriptions by means of C/C++ software implementations. These implementations are often huge and virtually impossible to be analyzed and manipulated without the aid of automated tools and appropriate methodologies. In many cases the understanding of the algorithms and the evaluation of their complexity and parallelization potential, are fundamental steps for correct architectural implementation choices.

Another important issue is that the interest in the network, multimedia, cryptographic and other fields is restricted to evaluations and measures under real input conditions, and not through strict worst case analysis that would lead to consider pathological cases far from the interest of real efficient implementation solutions.

It is also desirable to understand and measure the algorithm complexity and the parallelization potential at the highest possible algorithmic level. Such understanding at the very early stage is fundamental in order to be able to take meaningful and efficient partitioning decisions and bring them to actual efficient parallel implementations.

# 1.1.2. Critical path analysis problem

The problem of identifying one of the longest paths in a circuit or in a

program is called a critical path problem [41]. The critical path analysis is an efficient mechanism used at several levels of system design, including circuit-, logic-, architecture-, algorithmic-, and system-levels. At system level, the process of hardware/software partitioning is a complex optimization problem [21]. The final solution depends on a variety of design constraints/goals like performance, power consumption, implementation cost. The critical path analysis can be used for the detection of more efficient hardware/software partitions and their implementation parameters.

At circuit level, the length of critical path plays a key role in setting the clock cycle time and improving the architecture performance [41]. The critical path length is computed as the longest signal propagation delay in the circuit. In [41] the speed up of the critical path computation is achieved by means of parallel processing.

In designing VLSI or systems on chips architectures a complex computational task is represented as a directed task graph. The concept of critical path on the graph is used in [8] for solving the optimal buffer assignment problem by means of formulation of integer linear programming problem and decomposing the graph into a number of sub-graphs.

In high-level synthesis [43], the static data flow graph model is widely used for solving such tasks as scheduling, allocation and binding. During scheduling, the achievable iteration period is limited by the critical path time on the graphs. Some transformations are proposed in [43] on the static graphs in order to reduce the critical path time.

The idea described in [91] is to insert parallelism analysis code into the sequential simulation program. The execution of a discrete event simulation follows causality constraints, and the relationships between the events can be described by an event precedence graph. When the modified sequential program is executed, the time complexity of the parallel simulation is computed.

In [5] the critical path analysis is presented as a method for detailed understanding of when and how delays are introduced in data transfers in the Internet. By constructing and profiling the critical path, it is possible to determine what fraction of the total transfer latency is due to packet propagation, delays at the server and at the client, network variation etc.

In message passing and shared-memory parallel programs [22], communication and synchronization events result in multiple paths

through a program's execution. The critical path of the program is simply defined as the longest time-weighted sequence of events from the start of the program to its termination. The parallel computations are described by the program activity graph. The critical path of a parallel program is the longest path through the graph.

The critical path profiling is a metrics explicitly developed for parallel programs [22] and proved to be useful for several optimization goals. The critical path profile is a list of procedures and the time each procedure contributed to the length of the critical path. Critical path profiling is a way to identify the component in a parallel program that limits its performance. It is an effective metric for tuning parallel programs and is especially useful during the early stages of tuning a parallel program when load imbalance is a significant bottleneck. It also helps to find out, which components should be prioritized to terminate the program in time. Where an operation has to be completed on time, critical path analysis helps us to focus on the essential activities to which attention and resources should be devoted. Work [22] describes a runtime non-tracebased algorithm to compute the critical path profile of the execution of message passing and shared-memory parallel programs. This work also presents an online algorithm to compute a variant of critical path, called critical path zeroing, which measures the reduction in application's execution time after the elimination of a selected procedure.

The critical path analysis also gives an effective basis for the scheduling of computations. On multiprocessor system, task scheduling is important to achieve good performance. The work presented in [36] proposes a task scheduling algorithm that allocates tasks followed by correcting the critical path. The technique described in [38] schedules noncyclic non-branching task graphs, analyzing dynamically the critical paths in current schedule. Papers [61, 71] define the net schedule concurrency level with a set of pairs of operations to be executed in parallel. The techniques based on the minimization of critical path length that is estimated as the maximum clique weight of the sequential and parallel operator graphs constitute the most efficient approach to the generation of concurrent schedules.

#### 1.1.3. Parallelization potential of algorithm

The algorithmic complexity and parallelization potential that is hidden in an algorithm does not depend on the type of underlying hardware architecture and compiler technology which are used for the complexity evaluation. It depends on the algorithm itself and on input data that has to be processed to output data. This book focuses on the methodology for the measure of the critical path as evaluation of the parallelization potential of algorithms / architectures that are described /modeled using a high level programming or hardware description language. Despite the approach could in principle be applied to any programming language, the implementation using an automatic instrumentation stage presented here has been studied and developed for C language.

#### 1.2. Methodology of evaluating algorithm critical path

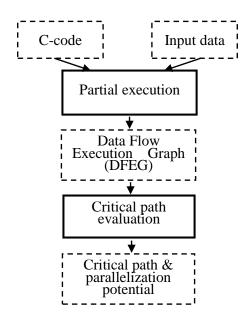

This chapter presents a methodology for evaluating the critical path on the Data Flow Execution Graph (DFEG) of algorithms specified as C programs. It proposes an efficient dynamic critical path evaluation approach that generates dynamically a data flow execution graph. Such an approach includes two key stages: (1) the instrumentation of the C code and mapping it into a C++ code version, (2) the execution of the C++ code under real input data and dynamically evaluating the actual critical path. The methodology and tools of analyzing algorithms / programs aim at the estimation and increase of the upper bound of the execution speed and parallelization potential of algorithms. The methodology is particularly tailored for application to multimedia, cryptographic and other complex algorithms. Critical path analysis and the subsequent algorithmic development stage is a fundamental methodological preliminary step for the efficient definition of architectures when the objective is the implementation of the multimedia algorithms on parallel homogeneous and heterogeneous platforms.

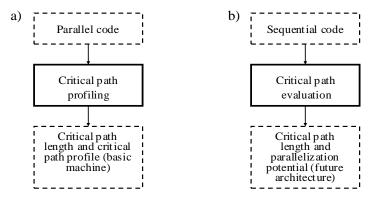

Summarizing the previous results, we can conclude that the majority of already developed methodologies and tools aim at the critical path profiling for tuning existing parallel programs executed on basic machines (Fig. 1a). In this paper, the objective is to propose a critical path model metrics that can be obtained using automatic evaluation tools such

as the one described in [75, 83] in order to be able to find out in which degree a given algorithm described in the C language satisfies the parallel implementation conditions (Fig. 1b). Analyzing the measures of the critical path obtained from simulation results using an automatic instrumentation tool, the most promising algorithms, from the parallelization point of view, can be selected among many alternatives. Moreover, the equivalent transformation of algorithms reducing the critical path and increasing the possible acceleration of the future parallel architecture can be performed.

The following principles constitute a basis for the methodology of the critical path evaluation:

- 1. The critical path is defined on the C-code's data flow execution without taking into account the true control flow;

- 2. The critical path length and the system parallelization potential are defined in terms of the complexity of C language basic operations (including *read* and *write* operations). The parameters of the machine executing the instrumented C-code during evaluating the critical path are not taken into account

- 3. In the definition of the critical path, the Data Flow Execution Graph results from the partial computation of the C-code using true input data. Therefore, such Data Flow Execution Graph is used for the critical path definition instead of the traditional static Data Flow Graph.

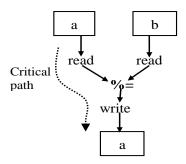

Figure 1.1. Critical path profiling (a) of parallel code on event graphs versus critical path evaluation (b) of sequential code on data dependences graphs

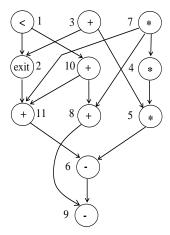

### 1.2.1. Data Flow Execution Graph

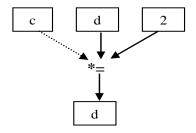

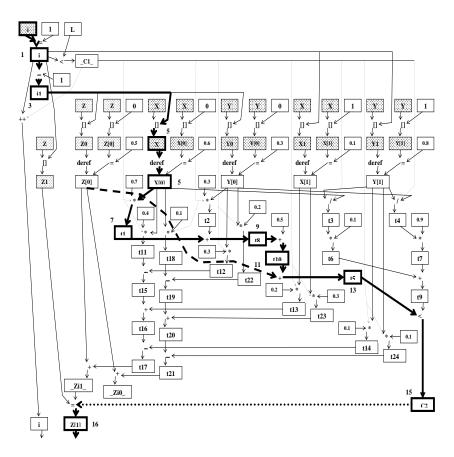

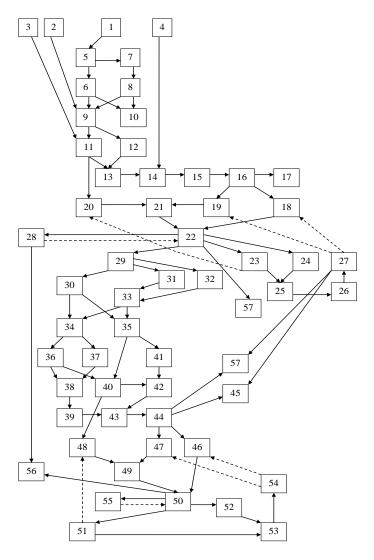

The DFEG is represented as a finite non-cyclic directed weighted graph constructed on the two types of node. The first type includes name-, address-, and scalar value-nodes. The second type includes operator-nodes. The name- and address-nodes are represented as and the i. The operator-nodes are denoted value-nodes are represented as L using the usual C-language notation: =, [], ++, --, +, \*, %, ==, /=, <, >, +=, /=, read (r), write (w) and others. The graph nodes may be connected by two types of arc: the data dependence arc denoted - and the conditional dependence arc denoted ——. The data dependence arc connects input names, addresses and values with an operator and connects an operator with its output value or address. The conditional dependence arc connects a test value with an operator or value covered by a conditional instruction. A graph node without incoming arcs is called an initial node and a graph node without outgoing arcs is called a final node. A DFEG fragment for if (c) d\*=2; C-code is shown in Fig. 1.2. It contains four value-nodes, one operator-node, three data and one conditional dependence arcs.

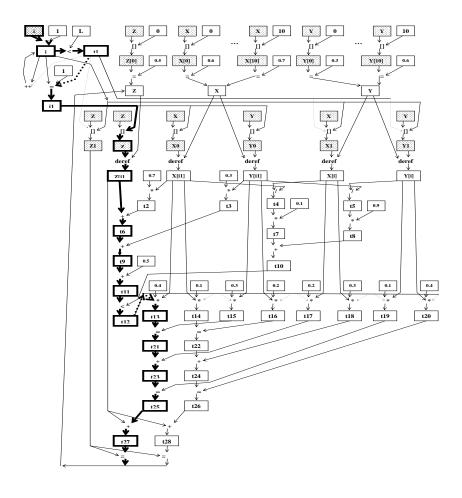

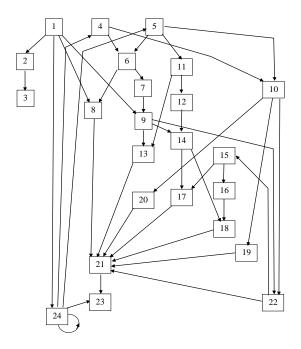

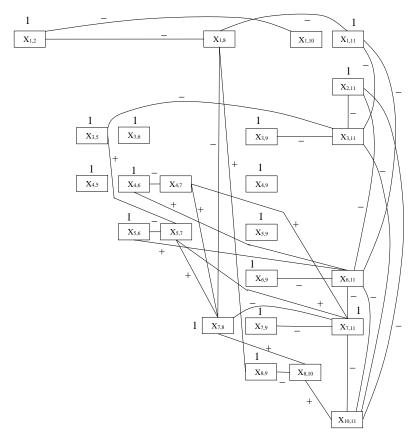

An example C-code for recurrent computations is presented in Fig. 1.3. The static DFG for the code is shown in Fig. 1.4. The corresponding dynamic DFEG for the first iteration of the loop is shown in Fig. 1.5. The array components are treated as separate scalar elements. The DFEG includes all types of name-, address-, and value-nodes as well as the various operator-nodes (*deref* is an implicit dereference operator).

Figure 1.2. Example DFEG fragment for if(c) d\*=2; C-code

Figure 1.3. An example C-code for recurrent computations

#### 1.2.2 Computational complexity of data flow execution graph

The complexity of static DFG is traditionally evaluated as a sum of node (in particular operator-node) weights. If we assume that the weight of each operator-node equals 1, then the static complexity of the DFG presented in Fig. 1.4 equals 81. It is obvious this is the complexity of the algorithm description rather than the computational complexity of the algorithm.

The computational complexity of the algorithm can be evaluated on DFEG. The DFEG is weighted with the node complexities. All the complexities are accumulated at the operator-nodes and represent each C-operator by a fragment in the DFEG as shown in Fig. 1.6. A *read* operator is associated with each incoming arc of the operator-node and a *write* operator is associated with its outgoing arc. The complexity of the fragment in Fig. 1.6 is equal to 4 basic operators.

Similarly, assume that each basic operator complexity be equal to 1. Table 1.1 represents the C-language operator complexities. When the basic operator complexities are different, the table can be easily modified to map the critical path length on any target architecture.

The results of the complexity evaluation of the algorithm DFEG fragment shown in Fig. 1.5 are reported in Table 1.2. The overall complexity is of 97 basic operators. The implicit dereference operator complexity is assumed here to be equal to 0.

Figure 1.4. The static DFG for the C-code shown in Fig. 1.3. The algorithm description complexity equals 81 operator-nodes. The static critical path is shown in bold.

The critical path length equals 14 operator-nodes

Figure 1.5. The DFEG fragment for C-code shown in Fig. 1.3. The nodes generated during first iteration of the loop are presented. The critical path is in bold. The computational complexity of C-code is estimated through the number of nodes in DFEG. These are name-, value-, and operator-nodes. The data dependences are represented by lines and the conditional dependences are represented by dashed lines

#### 1.2.3 Critical path on data flow execution graph

In literature [43, 52], the concept of static critical path is defined on DFG as a simple critical path and a loop critical path. The objective is to minimize the iteration period during scheduling and resource allocation in high-level VLSI synthesis by means of unfolding, retiming, and pipelining transformations.

The essential drawback of this concept is that the minimum execution time and computational complexity of the overall algorithm cannot be estimated and exploited.

Figure 1.6. Evaluation of the complexity of a%=b; C-code

Table 1.1 Complexity and critical path length of C language operators

| Operation       | Operator           | Complexity | Critical path |

|-----------------|--------------------|------------|---------------|

| Assignment      | =                  | 1          | 1             |

| Reference       | &                  | 2          | 2             |

| Dereference     | *                  | 2          | 2             |

| Arithmetic      | +, -, *, /, %      | 3          | 2             |

| Arithmetic-     | +=, -=, *=, /=, %= | 4          | 3             |

| assignment      |                    |            |               |

| Subscript       | []                 | 3          | 2             |

| Increment (dec- | ++,                | 3          | 3             |

| rement)         |                    |            |               |

| Unary minus     | -                  | 2          | 2             |

| and others      |                    |            |               |

Table 1.2

Evaluation of the complexity of graph shown in Fig. 1.5

| Operator | Operator complexity | Number of operators | Total complexity |

|----------|---------------------|---------------------|------------------|

| =        | 1                   | 7                   | 7                |

| []       | 3                   | 8                   | 24               |

| <        | 3                   | 2                   | 6                |

| ++       | 3                   | 1                   | 3                |

| *        | 3                   | 8                   | 24               |

| /        | 3                   | 2                   | 6                |

| _        | 3                   | 3                   | 9                |

| +        | 3                   | 6                   | 18               |

$\Sigma = 97$

The critical path on the DFEG is defined as a sequence of the graph nodes with the maximal sum of weights connecting an initial node with a final node. The internal critical path length on the graph fragment shown in Fig. 1.7 equals 3 because two *read* operations are executed in parallel. Similarly, Table 1.1 represents internal critical path lengths of the Clanguage operators.

Figure 1.7. Evaluation of the critical path on a%=b; C-code

In Fig. 1.5, address- and value-nodes are weighted with external critical path lengths. The critical path on the DFEG for the first iteration of the loop is shown in bold.

The critical path length equals 28. The maximum path length between Z[0] and Z[1] value-nodes equals 19. The nodes describe data depend-

ences between neighbor iterations of the loop and influence of the overall critical path length on the C-code that allows several iterations of the loop. It should be mentioned that the portion of the overall critical path in the DFEG fragment is not the same as shown in bold.

#### 1.2.4 Parallelization potential and feasible acceleration

The C-code computational complexity together with the critical path length in DFEG defines the parallelization potential of the algorithm:

Parallelization\_Potential = Complexity / Critical\_Path\_Length.

The algorithm parallelization potential aims at searching for an efficient parallel implementation of the C-code. It describes the possible acceleration that can be achieved due to a parallel implementation of the algorithm instead of the sequential implementation, but it does not describe the way of construction of such a parallel architecture. Various parallel implementations are possible for the same C-code. The acceleration due to parallelization depends on input data. Different input data imply different possible acceleration of the C-code. The parallelization potential is an upper bound for a non-pipelined architecture. Intermediate parallelization can be considered depending on the constraints on computing resources.

The estimated acceleration can be used in two ways:

- For creating a parallel version of the algorithm

- For reducing the C-code complexity and its critical path or developing a better C-code (algorithm)

The parallelization potential estimates the degree of possible reduction of the execution time due to parallelization of the overall computations associated with the given C-code and input data. Note that the definition of parallelization potential becomes illegal in case the description of complexity and critical path on static DFG such as defined in [43, 52] is used:

- The static DFG in [43, 52] is a very specific model not capable of representing most of algorithm descriptions in C-codes, assuming in particular there are no mutually exclusive branches on DFG

- The description complexity of DFG can be a basis for the estima-

- tion of the algorithm computational complexity in specific non numerous applications

- The static critical path time represents the iteration period and is not capable of evaluating and reducing the overall execution time of algorithms in the general case.

For the C-code shown in Fig. 1.3 and for the DFEG's fragment presented in Fig. 1.5, the algorithm complexity for the first iteration is equal to 97 and the critical path length is equal to 28. Therefore, the parallelization potential of the C-code portion is equal to 3.5.

# 1.3 Evaluation of computational complexity and critical path on data flow execution graph

# 1.3.1 Explicit evaluation of critical path

One approach to evaluating the critical path length consists in the preliminary generation of the DFEG by means of performing partial computations on the C-code's DFG (Fig. 1.8) under certain meaningful input data. The partially computed flow graph finally contains the operators associated with the scalar operands (values, addresses and variables) and does not contain elements associated with the true control structures. All scalar operands and operators remain in the DFEG.

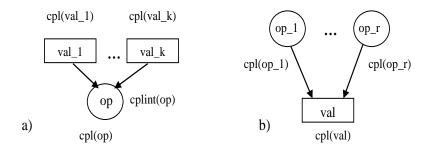

Given the complexity and internal critical path length of each operator-node in the DFEG, we can evaluate the external critical path for each address-, value- and operator-node in DFEG using the following simple recursive technique:

- 1. If val is an initial name-, address- or value-node then its external critical path length cpl(val)=0.

- 2. If *val* is a value- or address-node and *op\_1,...,op\_r* are operator-predecessors of *val* (Fig. 1.9b), then its critical path length *cpl(val)* =  $max(cpl(op\ l),...,cpl(op\ r))$ .

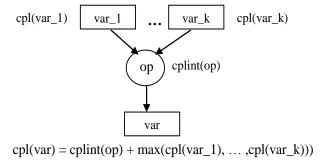

- 3. If op is an operator-node and  $val_1,...,val_k$  are value-address-predecessors of op (Fig. 1.9a), then the operator critical path length is  $cpl(op) = cplint(op) + max(cpl(val_1),...,cpl(val_k))$ , where cplint(op) is the op operator's internal critical path length.

Figure 1.8. Critical path evaluation by means of explicit generation of DFEG

Figure 1.9. The graph fragment (a) for evaluating the critical path for an operator and the graph fragment (b) for evaluating the critical path for a value (address)

The technique itself is very efficient, although it cannot be practically used. Its drawback is that the DFEG can result to a large graph that is

difficult to handle. Fig. 1.5 illustrates the evaluation of critical path on the explicitly generated DFEG. The evaluation procedure starts at the initial nodes and step by step using the above listed rules computes the external critical path length for each address- and value-node. The critical path for the Z[1] value-node is the overall critical path on this DFEG.

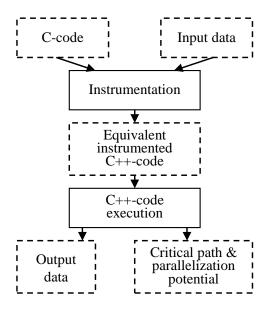

### 1.3.2 Dynamic evaluation of critical path

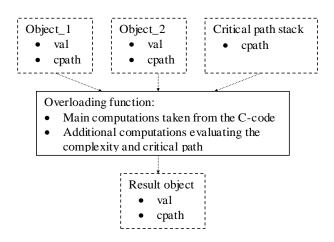

Since the number of nodes in the DFEG is equal to the number of operation calls during the program's execution, explicitly building the graph is not practical for long running programs. One way to overcome this limitation is to develop a technique that does not require building the graph. Such a technique is based on the flow shown in Fig. 1.10. Firstly, the C-code is instrumented by overloading all explicit and implicit operators [83] and is transformed into an equivalent C++-code, in terms of the operators applied to the input data. Secondly, the C++-code is executed under the given input data, computing output data and evaluating the complexity, critical path and parallelization potential of the algorithm.

In the C++-code, an additional *cpl* variable is associated with each actual scalar *var* variable (a separate variable, a scalar element of an array, a scalar element of a structure and so on) of the C-code (Fig. 1.11).

The execution of a C-code operation also results in computing a new value of the associated variable. The *cpl* variable describes the external critical path length for the main *var* variable. The computation of *cpl* is coupled with the computation of *var*. The performance of *op* operator results in computing the value of *var*, re-computing the algorithm complexity, and computing the *cpl* for *var*.

# 1.4 Tool for estimation of algorithm parallelization potential

# 1.4.1 Instrumenting and mapping the C-code onto a C++-code

The dynamic evaluation of the critical path as described in the previous section is useful if the program can be appropriately instrumented and mapped using automatic tools into an equivalent version of the code, thus avoiding annoying and resource consuming code rewriting.

Figure 1.10. Dynamic evaluation of the critical path by means of instrumenting and executing the C-code

Figure 1.11. General scheme for the dynamic evaluation of the critical path

This section provides an example of how such mapping can be implemented. More details of one possible implementation of such non trivial mapping can be also found in [83]. During the mapping of the source C-code into a C++-code version, the following parts of the C-code have to be instrumented to evaluate the parallelization potential of the algorithm:

- Data types and data objects

- Operators

- Control structures

- Functions

So as to correctly accomplish the evaluation, global and local additional variables and objects can be used in the instrumented C++-code. Global variable declarations can be as follows:

```

static unsigned long Algorithm_Complexity = 0;

static unsigned long Critical_Path_Length = 0;

static Critical_Path_Stack _CPS_;

```

where *Critical\_Path\_Stack* is a class implementing the mechanism of processing of conditional dependences associated with the nested control structures. An additional class object and its internal data elements can be associated with each scalar variable of the C-program. The C++-code in Fig. 1.12 will be used in this Section to illustrate and explain the key solutions taken during mapping the C-code into an equivalent C++-code.

The basic types of the C language such as *char*, *int*, *float*, *double*, *signed char*, *unsigned char*, *short int*, *long int*, *unsigned short int*, and others can be mapped into the classes with similar names CHAR, INT, FLOAT, DOUBLE, SIGNEDCHAR, UNSIGNEDCHAR, SHORTINT, LONGINT, UNSIGNED SHORTINT and others in the C++ language. The structure of the INT class in C++ for the *int* basic type of C is shown in Fig. 1.13. The *val* data element of the *int* type represents a variable in the source C-code. The *cpath* data element of the *unsigned long* (*double*) type describes the external critical path length for the *val* variable.

The class functions overload the operators on the data elements. Fig. 1.12 illustrates the way in which variables i and il of type int (Fig. 1.3) can be replaced with the same name objects of class INT.

```

#define L 10

void main() {

CRITICAL PATH TURN ON

FLOAT X[L]={0.6F, 0.1F, 0.9F, 0.3F, 0.8F, 0.5F, 0.7F, 0.2F, 0.4F, 0.7F};

FLOAT Y[L]={0.3F, 0.8F, 0.4F, 0.2F, 0.1F, 0.9F, 0.5F, 0.7F, 0.1F, 0.6F};

PointerPrih<FLOAT> Yp=Y;

PointerPrih<FLOAT> Xp=X;

FLOAT Z[L];

PointerPrih<FLOAT> Zp=Z;

Zp[0]=0.5F;

for(INT i=1; PUSH_LOOP(i < L); i++, POP1) { INT i1=i-1;

FLOAT& Z0=Zp[i1]; FLOAT& X0=Xp[i1]; FLOAT& Y0=Yp[i1];

FLOAT& Y1=Yp[i];

FLOAT& Z1=Zp[i];

FLOAT& X1=Xp[i];

if(PUSH IF((Z0 + X0*0.7F + Y0*0.3F + 0.5F) < ((X1/X0)*0.1F + (Y1/Y0)*0.9F)))

Z1=Z0 + X0*0.4F - Y0*0.3F + X1*0.2F - Y1*0.1F; else

Z1=Z0 + X0*0.1F - Y0*0.2F + X1*0.3F - Y1*0.4F;

POP1:

}

CRITICAL PATH TURN OFF

```

Figure 1.12. Example of a possible C++ instrumentation of the C-code shown in Fig. 1.3

```

class INT {

int val;

unsigned long cpath;

public:

constructor & destructor functions

functions for overloading operators

critical path stack functions

other functions

};

```

Figure 1.13. Example of possible mapping of the C's *int* basic data type to the INT class in C++

```

template <class IT> class PointerPrih {

IT * val;

unsigned long cpath;

public:

constructor & destructor functions

functions for overloading operators on pointers

critical path stack functions

other functions

};

```

Figure 1.14. Example of a possible instrumentation of the C's pointers in C++

Declarations of pointers to basic types *char*, *int*, *float*, *double*, etc. in C-code can be replaced by the *PointerPrih* classes defined for CHAR, INT, FLOAT, DOUBLE, and other instrumented types. The single template presented in Fig. 1.14 can generate all the classes, where IT denotes an instrumented type.

An array of elements of a basic type in the C-code can be mapped to an array of objects of the corresponding instrumented class in the C++code. In order to be able to count operations on the arrays including the [] subscript operation, a mechanism of instrumented pointers can be used. An appropriate instrumented pointer can be introduced for each array in the C++-code. All the operations to be executed on the array in the C-code are associated with the pointer in the C++-code. For example, the X, Y, and Z arrays of *float* type in Fig. 1.3 can be replaced with the X, Y, and Z arrays of objects of the FLOAT class in Fig. 1.12. Moreover, the Xp, Yp, and Zp instrumented pointers of the Pointer-Prih<FLOAT> class are introduced in the C++-code. After that, all array operations are executed on the pointers. Other composite types of C language can be instrumented in the similar way in C++ language.

All the operations on addresses and values that will be performed during the C-code execution stage are instrumented during transition from the C-code to the C++-code. Each operator in the C-code is overloaded by an appropriate class function in the C++-code (Fig. 1.15). The operators on the C-types are replaced with operators on the C++-classes. The overloading functions are defined for groups of close operators.

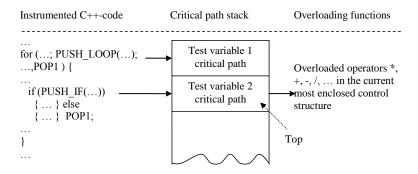

The true control structures are not taken into account during evaluating the critical path. The only influence of the structures on the DFEG is through the conditional dependences. A critical path stack is introduced in the instrumented C++-code in order to find out the dependences. The external critical path length of the declared or temporary T test variable is an element of the stack record.

A new record is added to the stack by the functions PUSH\_LOOP (T), PUSH\_IF(T), and PUSH\_SWITCH(T) presented in Table 1.3 and overloaded for each instrumented basic type by means of the member function *push(cpath)* of the \_CPS\_ object of the Critical\_Path\_Stack class. Functions PUSH\_LOOP and PUSH\_IF return a value of the *bool* type. The difference between the functions is that PUSH\_IF adds a record to the stack in any case not depending on its return value.

Figure 1.15. Overloading a binary operator by a class function

Table 1.3 **PUSH and POP macros/functions on the critical path stack**

| N | Function/Macro  | Return type  | Description              |

|---|-----------------|--------------|--------------------------|

| 1 | PUSH_IF(Test)   | bool         | push in _CPS_            |

| 2 | PUSH_SWITCH(Se) | type of Se   | push in _CPS_            |

| 3 | PUSH_LOOP(Test) | bool         | push in _CPS_ when true  |

| 4 | PUSH(CPlen)     | void         | push CPlen in _CPS_      |

| 5 | POP(N)          | void         | pop N records of _CPS_   |

| 6 | POP1            | void         | pop 1 record POP(1)      |

| 7 | POP_(Expr)      | type of Expr | POP(1) and transmit Expr |

| 8 | POP_(N, Expr)   | type of Expr | POP(N) and transmit Expr |

The PUSH\_LOOP function updates the stack when the return value equals *true* and does not update the stack when the value equals *false*. The return value type of PUSH\_SWITCH function is the same as the basic type of T argument. The function always adds a record to the stack.

The top records are removed from the stack by the macros/functions presented in Table 1.3. The macros/function POP(N) belongs to the critical path stack object \_CPS\_, where N is the number of records to be removed. The value of N equals 1 for *loop- if-* and *switch-*statements. It

can be greater than 1 for *break-continue-* and *return-*statements. A conditional ternary (T?TE:FE) operator is instrumented as POP\_(PUSH\_IF(T)?TE:FE) where TE and FE are expressions executed when test expression T is evaluated to *true* and *false* respectively, and POP\_ removes exactly one record from the stack and transmits the operator value. In general case, a *goto* statement makes the use of PUSH and POP functions illegal. The *goto* statements can be eliminated from the C/C++-code by equivalently transforming the unstructured program to a structured one. The mapping rules between C and C++ code versions for control structures are shown in Table 1.4, where *Stat* is a statement.

Fig. 1.16 presents an example of the mechanism of interaction of the instrumented control structures (Fig. 1.12) and the overloaded operators by means of the critical path stack. It is easy to see that the top *cpath* value is always larger than the previous ones in the stack.

The C-function bodies do not constitute a boarder for the data and conditional dependences among external and internal variables. The dependences are transmitted from the external environment to the function body and from the function body to the external environment by means of function's arguments and the return value of instrumented types.

The critical path can be evaluated for any part (parts) of the C-code. They should be described as a separated region by two macros: CRITICAL\_PATH\_TURN\_ON and CRITICAL\_PATH\_TURN\_OFF.

The C++-code that is out of the region simply transmits the variable critical path lengths. Thus, the critical path on the key functions of C code can be evaluated.

# 1.5 Reduction of critical path and increase of parallelism

## 1.5.1 Reduction by transformation of C/C++-code

The true control structures of the C-code are an obstacle in the direct implementation of parallelization potential and possible acceleration [69, 70]. The transformation methodology is a mechanism of searching for an appropriate architectural implementation [7, 16, 19]. It allows the reduction of execution time (iteration period, control steps and clock cycles) at the same constraints on resources and approaches the actual acceleration to the upper bound.

$\label{thm:control} Table~1.4$  Mapping of C control structures to C++ instrumented structures

| Control structure in C                                                         | Instrumented structure in C++                                                                                  |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| if, ?:, switch,                                                                | while, do, for                                                                                                 |

| if (TestExpr) ThenStat                                                         | if (PUSH_IF(TestExpr)) ThenStat POP1;                                                                          |

| if (TestExpr) ThenStat else ElseStat                                           | <pre>if (PUSH_IF(TestExpr)) ThenStat else ElseStat POP1;</pre>                                                 |

| Var = (TestExpr) ? TrueExpr : FalseExpr;                                       | Var = POP_((PUSH_IF(TestExpr)) ?<br>TrueExpr : FalseExpr);                                                     |

| switch (Select) {   case IntVal1: Stat1 break;   case IntVal2: Stat2 break;    | switch (PUSH_SWITCH(Select)) {   case IntVal1: Stat1 break;   case IntVal2: Stat2 break;                       |

| default: Statn }                                                               | default: Statn } POP1;                                                                                         |

| while (TestExpr) Stat                                                          | <pre>while (PUSH_LOOP(TestExpr)) {Stat POP1;}</pre>                                                            |

| do Stat while (TestExpr)                                                       | PUSH(0) do Stat POP1; while (PUSH_LOOP(TestExpr))                                                              |

| for (Init; Cond; Step) Stat                                                    | for (Init; PUSH_LOOP(Cond); Step POP1) Stat                                                                    |

| break, continu                                                                 | e, return, goto                                                                                                |

| for (Init; Cond; Step) {Stat1 if (Test-Expr) {Stat2 break;} Stat3}             | for (Init; PUSH_LOOP(Cond); Step<br>POP1) {Stat1 if (PUSH_IF(TestExpr))<br>{Stat2 POP(2); break;} POP1; Stat3} |

| for (Init; Cond; Step) {Stat1 if (Test-Expr) {Stat2 continue;} Stat3}          | for (Init; PUSH_LOOP(Cond); Step POP1) {Stat1 if (PUSH_IF(TestExpr)) {Stat2 POP(2); continue;} POP1; Stat3}    |

| TypeFun NameFun (Arg1,, Argk) {Stat1 if (TestExpr) {Stat2 return Expr;} Stat3} | TypeFun NameFun(Arg1,,Argk) {Stat1 if (PUSH_IF(TestExpr)) {Stat2 return POP_(1,Expr);} POP1; Stat3}            |

| goto Label;                                                                    | The unstructured program is transformed to an equivalent structured one                                        |

Figure 1.16. Generation of the conditional dependences using the critical path stack

Two types of transformation are investigated in the context of architectural synthesis. The transformations of the first type aim at the reduction of the critical path. The critical path evaluation tool helps to localize the transformations. The transformations of second type aim at breaking the true control structures in order to increase the effectiveness of behavioral synthesis and scheduling techniques. The transformation methodology allows the architectural implementation of parallelization potential by means of C-code transformation. The transformations promote the approach of DFG to DFEG.

The equivalent transformation of the source program is also a way of achieving the reduction of the critical path length and the increase of the parallelization potential of the C-code. No specific coding style is needed during creation of the source C-code, although the transformation itself may require specific code forms. The control and data flow transformation rules which are useful in the context of DFEG-based critical path reduction are as follows:

- Restructure, split, and transformation of statements

- Extraction of computations from control structures

- Algebraic transformation of arithmetic, logic and other type of expressions

- Merge of expressions and statements

- Unfolding loops and others.

Although most of the transformation rules have been previously considered in literature, these should be analyzed again in the context of dynamic global critical path definition and reduction on DFEG. For instance, the unfolding, retiming, and pipelining transformations aim at the reduction of iteration period on static DFG which cannot be less than the iteration bound [52]. Moreover the global critical path analysis helps to find places for the efficient application of the transformation rules.

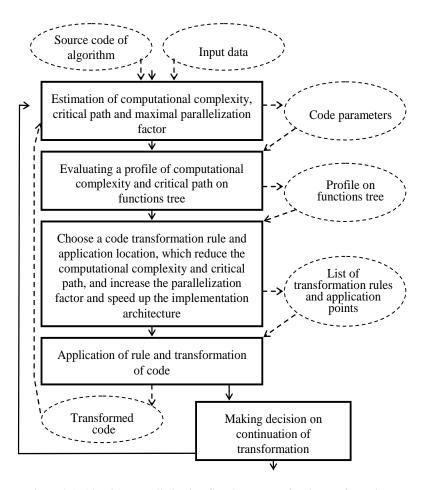

It can be noted that the procedure of increase of the parallelization potential of a C/C++-code is an iterative process. Firstly, the source C-code is transformed and rebuild. Then it is instrumented and mapped to a C++-code version using an automatic tool. After the execution of the C++-code using real input data as stimuli, evaluation of the critical path, estimation of the possible acceleration, and localization of further transformations, the intermediate C-code can then be transformed again in order to perform the next iteration.

## 1.5.2 Preliminary transformation of loops

In order to be able to apply other transformation rules to the C/C++-code, the loop statements should be preliminary transformed by means of moving the iteration scheme into the loop body. The *for*-loop

for

$$(T; D; S) \{ B \}$$

can be transformed to

$$for(T; ;) \{ \_C\_=D; if(\_C\_) \{ B S \} else break; \}$$

The while-loop

while

$$(D) \{ B \}$$

can be mapped to

while (true) {

$$\_C\_=D$$

; if ( $\_C\_$ ) {  $B$  } else break; }

The while-loop

```

do B while (D);

```

can be transformed to

```

do B _C=! D; if (_C) break; while (true);

```

After these transformations, the extraction of computations from control structures, and other types of transformation are possible.

### 1.5.3 Extraction of computations from control structures

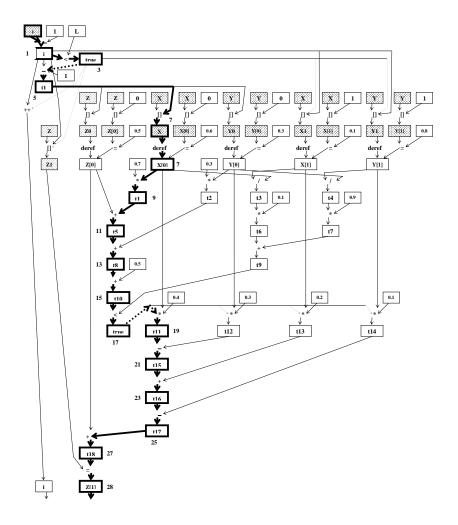

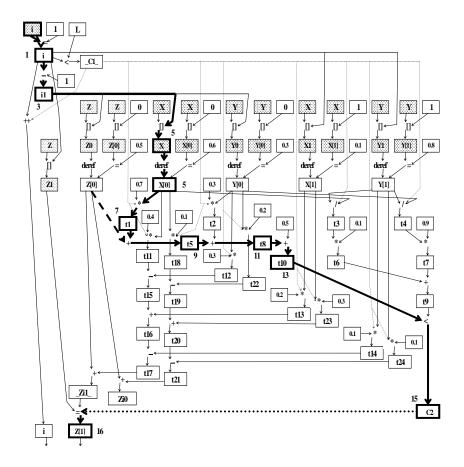

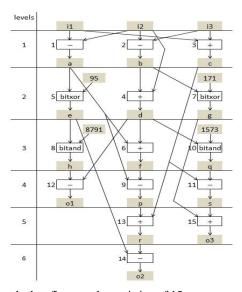

An efficient way of accelerating the computations is the extraction of operators from control structures and performing them in advance and in parallel. The extraction can follow the preliminary transformation of loops. Fig. 1.17 illustrates the extraction mechanism and transformation rules on the C-code presented in Fig. 1.3. The extraction implies the introduction of additional variables and computations. The critical path length for the first iteration of the loop is reduced from 28 to 16 while the complexity increases from 97 to 143 basic operations (Fig. 1.18). The maximum path length between the Z[i-1] and Z[i] value-nodes is equal to 9. The parallelization potential of the first iteration loop increases from 3.5 to 8.9.

Figure 1.17. Transformation of the C/C++-code shown in Fig. 1.3 (transformation of the *for*-loop and extracting computations from the *if-then-else*-statement)

Figure 1.18. The DFEG fragment (first iteration of the loop) for the transformed C/C++code shown in Fig. 1.17. The transformation is done by means of reconstruction

of the loop-statement and extraction of computations from if-statements. The graph

complexity implies the introduction of additional variables and computations.

The critical path length is in bold.

Fig. 1.19 presents the instrumented C++-code that performs the same basic computations as the source C-code and additionally providing its parallelization potential as result of the program execution grown compared to the non-transformed graph. The critical path shown in bold is reduced. The longest path between Z[i-1] and Z[i] nodes is also in bold.

```

#define L 10

void main()

CRITICAL PATH TURN ON

FLOAT X[L]={0.6F, 0.1F, 0.9F, 0.3F, 0.8F, 0.5F, 0.7F, 0.2F, 0.4F, 0.7F};

FLOAT Y[L]={0.3F, 0.8F, 0.4F, 0.2F, 0.1F, 0.9F, 0.5F, 0.7F, 0.1F, 0.6F};

PointerPrih<FLOAT> Xp=X;

PointerPrih<FLOAT> Yp=Y;

FLOAT Z[L];

PointerPrih<FLOAT> Zp=Z;

Zp[0]=0.5F;

INT _C1_=i < L;

for(INT i=1;;) {

INT i1=i-1;

FLOAT& Z0=Zp[i1];

FLOAT& X0=Xp[i1];

FLOAT& Y0=Yp[i1];

FLOAT& Z1=Zp[i];

FLOAT& X1=Xp[i];

FLOAT& Y1=Yp[i];

if(PUSH LOOP(C1)) {

INT C2 = (Z0 + X0*0.7F + Y0*0.3F + 0.5F) < ((X1/X0)*0.1F + (Y1/Y0)*0.9F);

FLOAT_Zi1_ = Z0 + X0*0.4F - Y0*0.3F + X1*0.2F - Y1*0.1F;

FLOAT_Zi0_ = Z0 + X0*0.1F - Y0*0.2F + X1*0.3F - Y1*0.4F;

if(PUSH IF(C2)) Z1= Zi1; else Z1= Zi0; POP1;

i++;

POP1:

} else break;

CRITICAL_PATH_TURN_OFF

}

```

Figure 1.19. Equivalent instrumented C++-code for the source code reported in Fig. 1.17 (Transf 1)

## 1.5.4 Transformation of expressions

The transformation of expressions is an efficient way of rebuilding the DFG and the DFEG of the C/C++-code. The objective of expression transformation is to rebuild the DFG in such a way as to reduce the number of operations on the critical path.

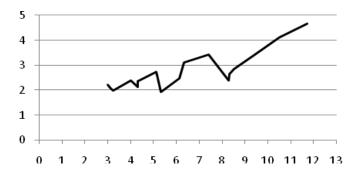

Fig. 1.20 presents a very simple transformation of expressions in the C/C++-code shown in Fig. 1.19. The transformation consists in changing the order of operation executions by means of using parenthesis. The transformed DFEG for the first iteration of the loop is presented in Fig. 1.21. The critical path length and the complexity of the loop's first iteration is the same as for the DFEG presented in Fig. 1.18. In the meantime, the maximum path length between the Z[i-1] and Z[i] value-nodes decreases from 9 to 5 basic operations. This implies the reduction in the total critical path length for many iterations of the loop.

Figure 1.20. Transformation and instrumentation of expressions (Fig. 1.18) in the C/C++-code (Transf\_2)

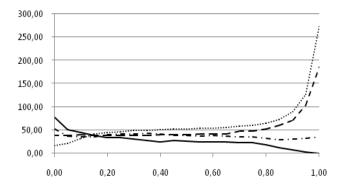

# 1.5.5 Effectiveness of transformations

Table 1.5 provides a comparison of the parallelization potential of three different C-codes (and instrumented C++-codes) with the same functionality. The number of executed iterations of the loop is the same and equals 10.

It is easy to see that the extraction of computations from control structures and the transformation of expressions imply significant increase in the algorithm execution acceleration and in the parallelization potential. The Transf\_1 performed by means of extraction of computations reduces the critical path length by 2.16 compared to the source code. The Transf\_2 performed by means of reordering of operator executions in expressions additionally reduces the critical path length by 1.44. The overall reduction constitutes 3.11.

In the meantime, some transformations can imply the increase in the C-code complexity. Thus, the extraction of computations in Transf\_1 implies the increase in C-code complexity by 1.3. The reasons are as follows:

- The reorganization of the C-code introduces additional variables and operators (operator executions)

- The extraction of computations from the if-statements implies the

execution of operators in any case not depending on the value of

test expressions; if the operators were under the control structures

it would not be necessary to execute some of them.

Figure 1.21. The DFEG illustrates reduction of the overall critical path length by means of transforming expressions. The reduction is obtained by reordering operators. The critical path is in bold. The distance between Z[i-1] and Z[i] nodes constitutes 5 operator-nodes instead of 9 operator-nodes in the previous DFEG

Table 1.5 **Parameters of the source and transformed C/C++-code**

| Algorithm | Complexity | Critical<br>path | Parallelization potential | Feasible acceleration |

|-----------|------------|------------------|---------------------------|-----------------------|

| Source    | 802        | 171              | 4.7                       | 1.00                  |

| Transf_1  | 1039       | 79               | 13.2                      | 2.16                  |

| Transf_2  | 1039       | 55               | 18.9                      | 3.11                  |

### 1.6 Evaluation accuracy and limitations

There are some assumptions implemented in the current dynamic critical path evaluation tool version. One of them is that a value-node in the explicitly generated DFEG can have more than one incoming arcs with weights (intermediate critical path lengths) to which the max-operation is applied. All the weights could be computed simultaneously in a parallel implementation version of the tool. But the implemented tool version runs on a single-processor machine and executes the instrumented C++code sequentially. Since only one additional critical path variable is associated with each main scalar variable, all the weights at the incoming arcs cannot be stored and processed simultaneously. The weights are processed sequentially, as the instrumented C++code is being executed. As a result the execution of the max-operation is broken into several steps which can imply some slight inaccuracy in the critical path measure.

The second assumption is that the C-code should not contain a variable representing several other different variables whose lifetimes are not intersected. The critical path length for this single variable would differ from the critical path length for the several separate variables due to the use of the max-operation. This is a source of inaccuracy in the critical path evaluation.

There are few limitations on the evaluation technique. One of the most significant takes place for data that are interpreted in different way by means of different types. For instance, the following two declarations

```

char* cvar = (char*) lvar;

cannot be legally instrumented and processed as

LONG lvar [] = {1, 3, 5, 7, 9, 15};

PointerPrih<CHAR> cvar = (CHAR*) lvar;

```

long lvar  $[] = \{1, 3, 5, 7, 9, 15\};$

However, the mentioned inaccuracies and limitations do not constitute a significant burden for most of the evaluations performed on complex multimedia algorithms. Some alternative implementation of the operators overloading capable of removing such limitations are under

study. The critical path evaluation tool has been successfully used for large programs such as Wavelet algorithm implementations, the MPEG-4 Optimized Reference Software, and the Cryptographic toolkit [72, 84] and others, without requiring any code rewriting.

#### 1.7 Conclusion

This chapter has presented a methodology for the measure of the parallelization potential of complex algorithms. The measure is based on the dynamic evaluation of the data flow execution graph and is performed by mapping a C-program into an instrumented C++ version, and then executing the equivalent C++ program under real input data. By combining critical path evaluations with code transformation techniques, an efficient methodology can be built for exploring parallel implementations of the algorithm, thus detecting efficient architectures the algorithm can be mapped to. The mapping from the C description to a C++ instrumented description that provides critical path measures can be done by an automatic software tool, avoiding resource consuming code rewriting.

Analyzing the obtained measures, for each methodological iteration, the most promising algorithms in terms of parallelization potential can be selected among many possible alternatives. Applying transformations to the algorithm and reducing the critical path length, thus further increasing the degree of parallelization, result very effective for the definition of efficient implementation architectures. The critical path length significantly influences the results of scheduling the implementations at several kinds of constraints on computational resources. The schedule cannot be faster than the critical path length. A systematic methodology for reduction of the critical path length guarantees more powerful scheduling results and implicitly provides improvements in the trade off "complexity—delay" that is common for software development, high-level synthesis and architecture design in various application fields.

# 2. PARALLELIZATION POTENTIAL OF MEANINGFUL HARDWARE / SOFTWARE APPLICATIONS

# 2.1. Parallelization potential of two-dimensional WAVELET codec

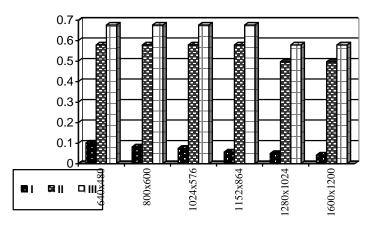

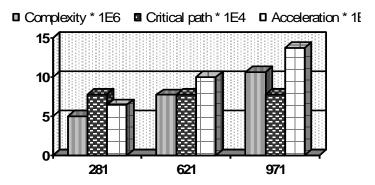

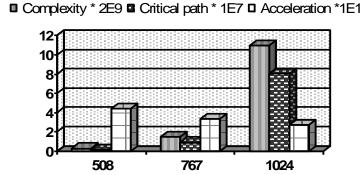

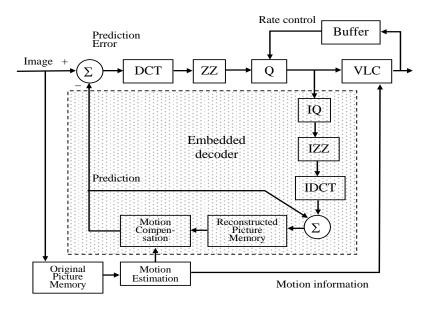

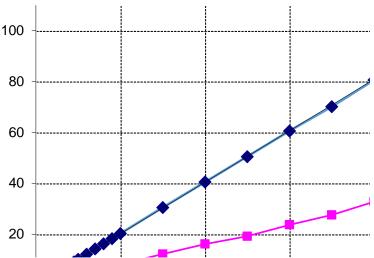

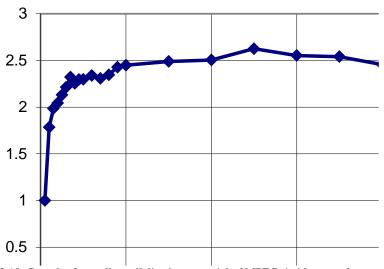

Impressive results on the parallelization potential have been obtained for the two-dimensional Wavelet codec implementations proposed in [83]. Tables 2.1, 2.2 and 2.3 report experimental results obtained on three versions of DFEG that are dynamically generated on different C-codes with the same functionality:

- DFEG of the original C-code as it was created (Case I)

- DFEG of Case I without nodes that describe control computations on the two dimensional array representing an image (Case II)

- The transformed C-code of Case II and its DFEG (Case III).

In Case I a portion of the C-code is responsible for global iterative traversal of the two dimensional array representing an image. In Case II the array is considered as a set of directly addressed and accessed separate scalar variables. The control computations associated with the iterative global traversal can be eliminated. An architecture which implements distributed on pixels computations can be generated. In Case III a C-code is obtained by means of transforming several expressions constituting the wavelet core.

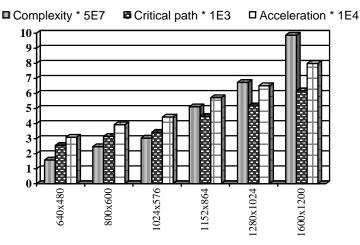

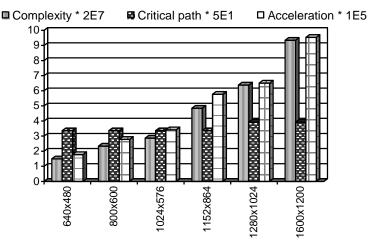

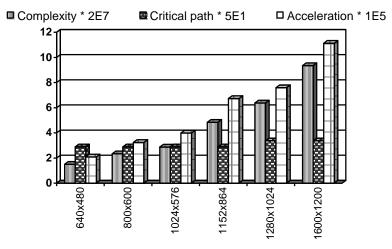

The algorithm computational complexity increases as the image size grows. It constitutes from 79 to 493 million operations for Case I and from 30 to 187 million operations for Cases II and III. The average number of operations executed per pixel equals 257 in Case I, and equals 97 operations in Cases II and III. The data flow computations to be incorporated in the C-code implementation constitute 37.9%, and the control flow computations constitute 62.1%.

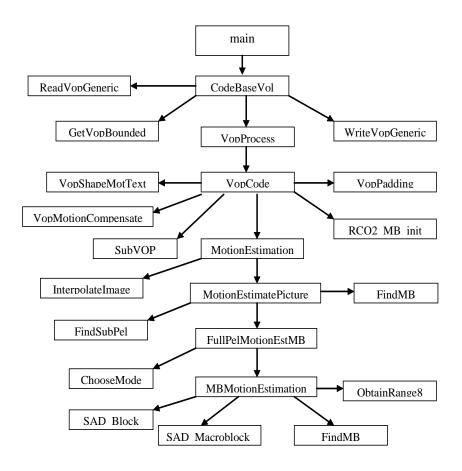

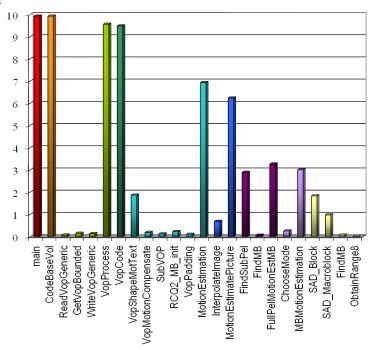

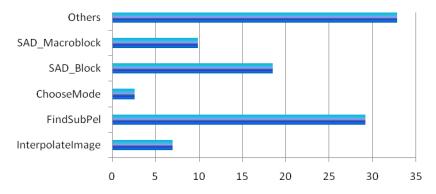

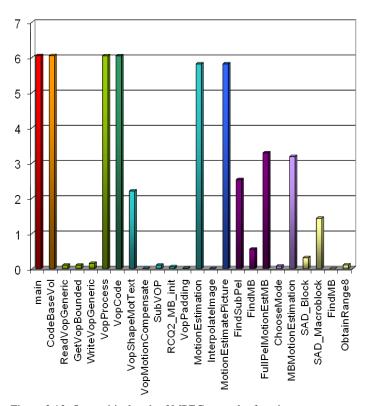

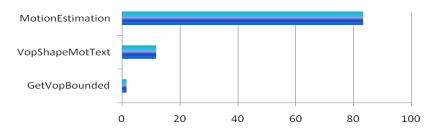

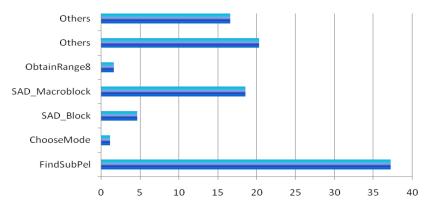

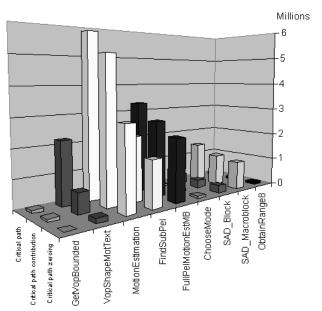

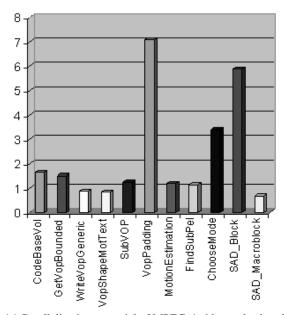

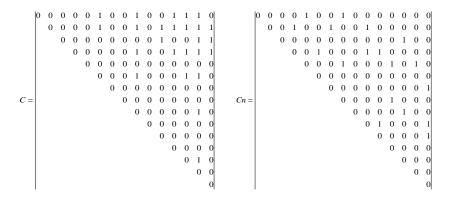

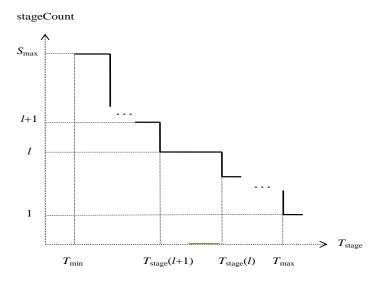

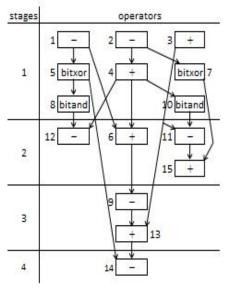

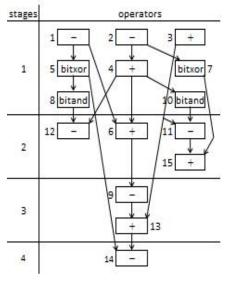

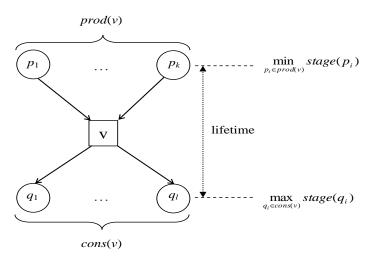

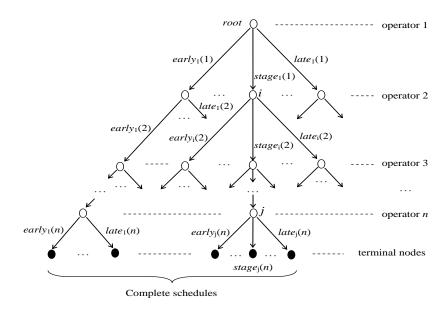

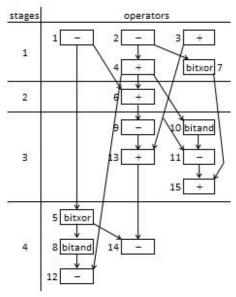

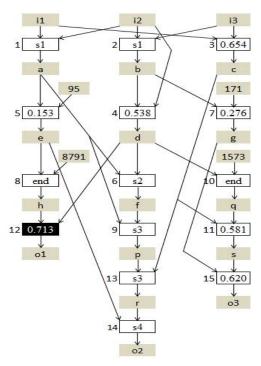

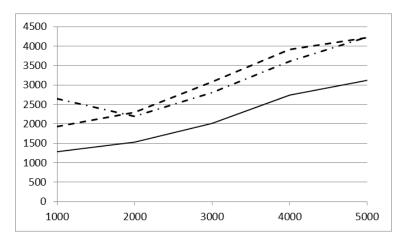

The increase in the image size implies the increase in the critical path length. The length varies in the range from 2.55 up to 6.17 thousand operations in Case I, in the range from 168 up to 196 operations for case II and in the range from 144 to 168 operations in Case III. After the equivalent transformation of WAVELET C-code and modifying its DFG (Case III), the critical path length has been reduced by 16.7% compared to Case II.