## МИНИСТЕРСТВО ОБРАЗОВАНИЯ РЕСПУБЛИКИ БЕЛАРУСЬ

# **Белорусский национальный** технический университет

# Кафедра «Робототехнические системы»

А. М. Капустина Ф. Л. Сиротин

# СИСТЕМЫ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ

Методическое пособие по лабораторным и практическим работам

> Минск БНТУ 2014

# МИНИСТЕРСТВО ОБРАЗОВАНИЯ РЕСПУБЛИКИ БЕЛАРУСЬ Белорусский национальный технический университет

Кафедра «Робототехнические системы»

А. М. Капустина Ф. Л. Сиротин

# СИСТЕМЫ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ

Методическое пособие по лабораторным и практическим работам для студентов специальностей 1-53 01 01 «Автоматизация технологических процессов и производств», 1-53 01 06 «Промышленные роботы и робототехнические комплексы»

Минск БНТУ 2014 УДК 621.9-05(075.8) ББК 34.5-7я7 К20

#### Рецензенты:

канд. техн. наук, зав. кафедрой «Электропривод и автоматизация промышленных установок и технологических комплексов» Г. И. Гульков;

канд. техн. наук, зав. кафедрой «Программное обеспечение вычислительной техники и автоматизированных систем» *Н. Н. Гурский*

#### Капустина, А. М.

К20 Системы управления технологическим оборудованием: методическое пособие по лабораторным и практическим работам для студентов специальностей 1-53 01 01 «Автоматизация технологических процессов и производств», 1-53 01 06 «Промышленные роботы и робототехнические комплексы» / А. М. Капустина, Ф. Л. Сиротин. – Минск: БНТУ, 2014. – 45 с. ISBN 978-985-550-205-1.

В издание включены методические рекомендации к лабораторным и практическим работам по дисциплине «Системы управления технологическим оборудованием».

Цель издания: приобретение студентами практических навыков использования теоретических методов анализа синтеза в построении функционально-логических схем автоматов по заданному закону функционирования.

УДК 621.9-05(075.8) ББК 34.5-7я7

ISBN 978-985-550-205-1

- © Капустина А. М., Сиротин Ф. Л., 2014

- © Белорусский национальный технический университет, 2014

## 1. СТРУКТУРНЫЙ СИНТЕЗ ДИСКРЕТНЫХ АВТОМАТОВ

Цель работы. Изучить методы и последовательность синтеза.

#### Последовательность синтеза

- 1. По заданному закону функционирования составляется таблица истинности.

- 2. По таблице истинности записывается переключательная функция  $\Pi\Phi$  (в СДНФ или СКНФ) в зависимости от того, какой сигнал нужно получить на выходе (I или 0).

- 3. ПФ минимизируется и переводится в совершенные нормальные формы базисов Пирса и Шеффера в зависимости от заданной элементной базы построения схемы.

- 4. Построение схемы (функционально-логической) автомата по ПФ выраженной в совершенной нормальной форме выбранного базиса (СДНФ или СКНФ).

Задание 1. Произвести синтез автомата сложения двух одноразрядных двоичных чисел, каждое из которых может принимать одно из двух возможных значений: "0" или "1". Сигнал на выходе должен быть равен единице только при наличии на входе нечетного числа ("1") единиц.

#### 1. Таблица истинности

| n     | 0 | 1 | 2 | 3 | Номера кодовых комбинаций             |

|-------|---|---|---|---|---------------------------------------|

| $X_2$ | 0 | 0 | 1 | 1 | V V oppression                        |

| $X_1$ | 0 | 1 | 0 | 1 | $X_1, X_2$ — аргументы $\Pi \Phi - v$ |

| $Y_1$ | 0 | 1 | 1 | 0 | $\Pi\Psi - y$                         |

2. По КЕ (конституантам единицы) составляется переключательная функция (П $\Phi$ ) в СДН $\Phi$

$$y = X_1 \cdot \overline{X}_2 \vee X_2 \cdot \overline{X}_1$$

3. Минимизации не подлежит.

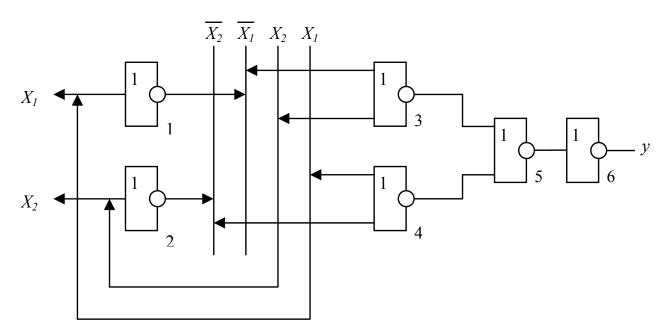

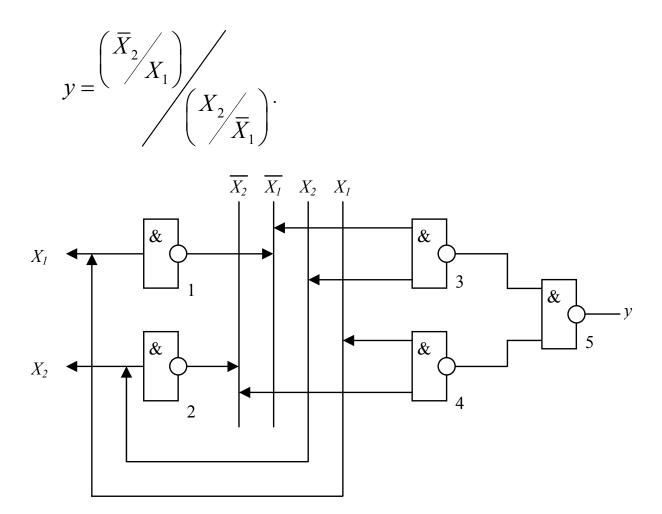

4. а) Если в базисе Пирса должна быть реализована схема автомата, то в этот базис переводятся сначала элементарные конъюнкции  $\Pi\Phi$

$$\overline{X}_2 \cdot X_1 = X_2 \downarrow \overline{X}_1; \qquad X_2 \cdot \overline{X}_1 = \overline{X}_2 \downarrow X_1,$$

а затем дизъюнкция заменяется функцией Пирса.

Тогда ПФ в базисе Пирса

$$y = \overline{\left(X_2 \downarrow \overline{X}_1\right) \downarrow \left(\overline{X}_2 \downarrow X_1\right)}.$$

Из выражения видно, что для схемной реализации надо иметь два инвертирующих элемента на входе схемы, три элемента реализующих функцию Пирса и один общий инвертирующий элемент.

б) Если в базисе Шеффера, то

$$\overline{X}_2 \cdot X_1 = \overline{\overline{X}_2 / X_1}; \qquad X_2 \cdot \overline{X}_1 = \overline{X_2 / \overline{X}_1};$$

Задание 2. Провести синтез сумматора.

Сумматор вырабатывает сигнал суммы у, и сигнал переноса у $_2$  в следующий двоичный разряд суммы при сложении трех двоичных чисел.

Задание 3. Осуществить синтез устройства по абстрактной таблице истинности.

# Способы задания дискретных автоматов с памятью

Основными задачами дискретных автоматов являются задачи анализа и синтеза.

Под анализом подразумевается определение закона его функционирования по уже разработанной конкретной функциональнологической схеме.

Синтез заключается в построении функционально-логической схемы автомата по заданному закону функционирования.

Два этапа решения задачи:

- 1. Абстрактный синтез (математическая модель)

- 2. Структурный синтез (кодирование математической модели и выражение ее реально существующими логическими элементами с помощью элементов выбранного и заданного базиса с последующим построением функционально-логической схемы автомата).

При синтезе дискретных автоматов без памяти задание закона функционирования достигалось при помощи таблиц истинности и переключательных функций, которые однозначно определяли значения выходных сигналов.

Для дискретных автоматов с памятью необходимо описать все элементы множеств  $\{X, Y, A, \delta, \lambda\}$ , т.е. входной и выходной алфавиты, алфавит состояний, а также функции переходов и выходов.

Наибольшее распространение получили способы:

- 1. Канонический (табличный, графический)

- 2. Граф-схем алгоритмов.

Выходной сигнал дискретных автоматов с памятью зависит не только от входного сигнала, поступившего в данный момент времени, но и от входных сигналов, поступивших в предыдущие моменты времени.

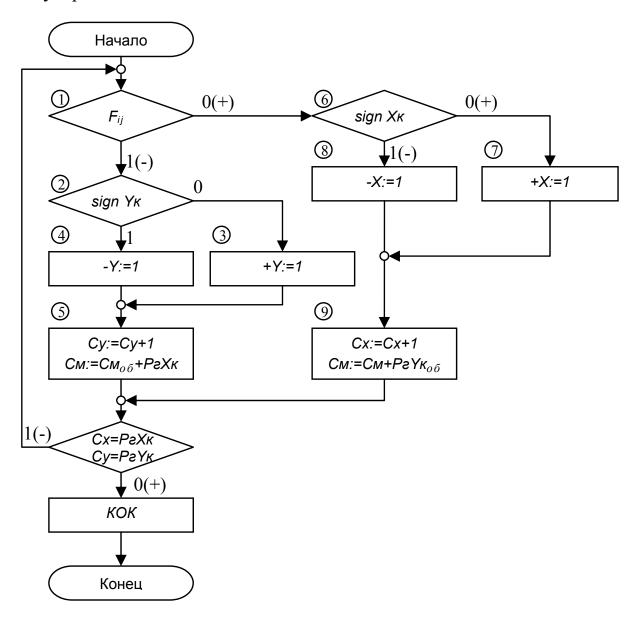

# Синтез линейного интерполятора

Составим блок-схему алгоритма работы линейного интерполятора. Блок-схема содержит регистры РгХ и РгҮ координат Хк и Үк конечной точки интерполяции прямой.

PrFij – регистр оценочной функции и счетчики Сх и Су значений текущих координат Xi и Yj.

См – сумматор и генератор синхроимпульсов на РгСт. Обработка очередного кадра программы интерполятора начинается с ввода в РгХ и РгУ значений величин и очищения регистров и счетчиков РгFij, Сх, Су.

Проанализируем работу интерполятора по методу оценочной функции при  $X\kappa = 7$  и  $Y\kappa = 5$ .

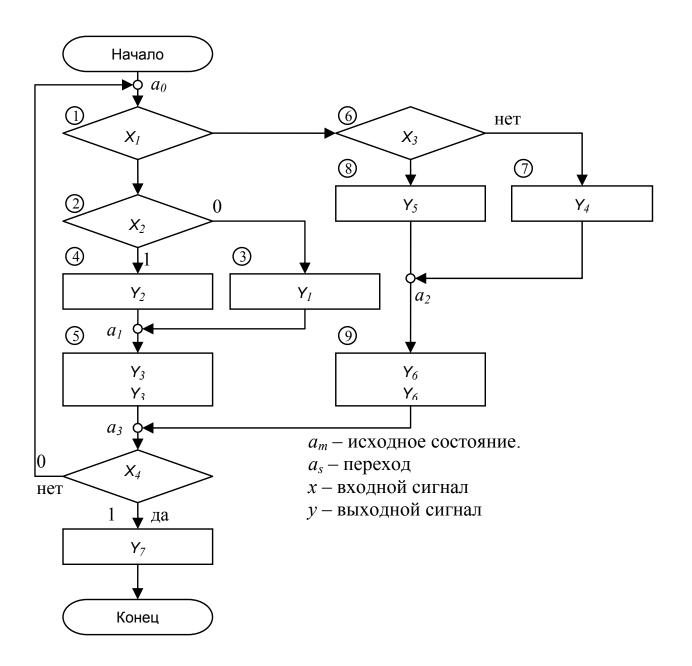

1. Составим граф-схему (рис. 1.2) по алгоритму (рис. 1.1) работы устройства.

Рис. 1.1. Алгоритм работы линейного интерполятора

Математически дискретные автоматы с памятью задаются пятью конечными множествами: входные сигналы  $X(x_1 \dots x_m)$ ; выходные  $Y(y_1 \dots y_n)$ ; внутренние состояния автомата  $A(a_1 \dots a_k)$ ; функции

переходов  $\delta$ , реализующие отображение множеств A и X в A. функции выходов  $\lambda$ , реализующие отображение множеств A и X в Y.

Рис. 1.2. Граф-схема алгоритма

- 2. С помощью первых трех множеств закодируем ее.

- 3. По закодированной граф-схеме составим таблицу переходов.

| No | a <sub>m</sub> | $a_{\rm s}$                            | x                                                                                          | у                                           |

|----|----------------|----------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------|

| 1  | $a_0$          | $a_1$ $a_1$                            | $\frac{x_1 x_2}{\overline{x}_2 x_1}$                                                       | <i>y</i> <sub>2</sub> <i>y</i> <sub>1</sub> |

| 2  | $a_0$          | $egin{array}{c} a_2 \ a_2 \end{array}$ | $ \begin{array}{ccc} \overline{x}_1 & x_3 \\ \overline{x}_1 & \overline{x}_3 \end{array} $ | <i>y</i> 5<br><i>y</i> 4                    |

| 3  | $a_1$          | $a_3$                                  | 1                                                                                          | <i>y</i> <sub>3</sub>                       |

| 4  | $a_2$          | $a_3$                                  | 1                                                                                          | <i>y</i> <sub>6</sub>                       |

| 5  | a <sub>3</sub> | $a_0$                                  | $\overline{x}_4$                                                                           | _                                           |

| 6  | $a_3$          | $a_0$                                  | $x_4$                                                                                      | <i>y</i> <sub>7</sub>                       |

Так как автомат имеет четыре состояния  $a_0$ ,  $a_1$ ,  $a_2$ ,  $a_3$ , то для их обеспечения необходимо иметь два запоминающих элемента.

Если в качестве кода использовать эквивалент его номера в двоичной системе счисления, а в качестве запоминающих — тактируемые "D"-триггеры, то структурная схема примет вид.

| Исход-<br>ное со-<br>стояние<br>а <sub>m</sub> | Код исх.<br>состоя-<br>ния<br>k (a <sub>m)</sub> | Состоя-<br>ние<br>перехода<br>а <sub>s</sub> | Код<br>k (a <sub>s)</sub> | Входной<br>сигнал<br>Х                                    | Выход-<br>ной<br>сигнал<br>Ү                | Функции возбуж- дения. $S(a_m, a_s)$   |

|------------------------------------------------|--------------------------------------------------|----------------------------------------------|---------------------------|-----------------------------------------------------------|---------------------------------------------|----------------------------------------|

| $a_0$                                          | 00                                               | $a_1$ $a_1$                                  | 01<br>01                  | $\frac{x_1 x_2}{\overline{x}_2 x_1}$                      | <i>y</i> <sub>2</sub> <i>y</i> <sub>1</sub> | $egin{array}{c} S_1 \ S_1 \end{array}$ |

| $a_0$                                          | 00                                               | a <sub>2</sub><br>a <sub>2</sub>             | 10<br>10                  | $ \overline{x}_4 \ x_3  \overline{x}_1 \ \overline{x}_3 $ | У5<br>У4                                    | $egin{array}{c} S_2 \ S_2 \end{array}$ |

| $a_1$                                          | 01                                               | a <sub>3</sub>                               | 11                        | 1                                                         | <i>y</i> <sub>3</sub>                       | $S_2$                                  |

| $a_2$                                          | 10                                               | a <sub>3</sub>                               | 11                        | 1                                                         | <i>y</i> <sub>6</sub>                       | $S_1$                                  |

| a <sub>3</sub>                                 | 11                                               | $egin{array}{c} a_0 \ a_0 \end{array}$       | 00 00                     | $\overline{x}_4$ $x_4$                                    | —<br>У7                                     | _                                      |

4. По структурной схеме составляются выходные функции (у): и функции возбуждения (S):

$$\begin{aligned} y_1 &= a_0 x_1 \cdot \overline{x}_2; \\ y_2 &= a_0 x_1 \cdot x_2; \\ y_3 &= a_1; \\ y_4 &= a_0 \overline{x}_1 \cdot \overline{x}_3; \\ y_5 &= a_0 \overline{x}_1 \cdot x_3; \\ y_6 &= a_2; \\ y_7 &= a_3 \cdot x_4; \end{aligned} \qquad \begin{aligned} S_1 &= y_1 \vee y_2 \vee y_6; \\ S_1 &= a_0 x_1 \overline{x}_2 \vee a_0 x_1 x_2 \vee a_2 = a_0 x_1 \vee a_2; \\ S_2 &= y_3 \vee y_4 \vee y_5; \\ S_2 &= a_0 \overline{x}_1 x_3 \vee a_0 \overline{x}_1 \overline{x}_3 \vee a_1 = a_0 \overline{x}_1 \vee a_1. \end{aligned}$$

## 2. ИССЛЕДОВАНИЕ СДВИГАЮЩИХ РЕГИСТРОВ

*Цель работы*. Ознакомление с принципами действия и функционально-логическими схемами сдвигающих регистров.

#### 1. Основные положения

Регистром называется устройство, предназначенное для запоминания слова, а также для выполнения над словом некоторых логических преобразований.

Регистр представляет собой совокупность триггеров, число которых соответствует количеству разрядов в слове, и вспомогательных схем, обеспечивающих в общем случае выполнение следующих операций:

- 1. Установка регистра в нуль ("сброс").

- 2. Прием слова из другого устройства (регистра, сумматора и т.д.).

- 3. Передача слова в другое устройство.

- 4. Преобразование кода числа (прямого кода в обратный и наоборот).

- 5. Сдвиг слова вправо или влево на требуемое число разрядов.

- 6. Преобразование последовательного кода слова в параллельный и наоборот.

- 7. Логическое сложение.

- 8. Логическое умножение.

- 9. Поразрядное сложение.

Схемы конкретных регистров могут допускать выполнение лишь некоторых из указанных выше операций.

В соответствии с указанными функциями регистры выполняются на триггерах с раздельными (установочными) входами. Приемом, выдачей и другими операциями в регистре управляют специальные сигналы, поступающие по управляющим шинам на входные и выходные вентильные (клапаны) схемы триггеров регистра. Операцию передачи кода слова в регистр и из регистра можно осуществлять параллельно или последовательно.

При последовательной передаче кода слова все разряды передаются последовательно во времени один за другим. При параллельной передаче кода слова все его разряды передаются одновременно, каждый по своей цепи.

Рассмотрим реализованный в системе алгоритм преобразования двоично-десятичного кода в двоичный. Это преобразование сведено к последовательному выполнению операции деления на два (т. е. сдвигу вправо на один разряд) с последующей коррекцией соседних разрядов с учетом переноса. Число тактов преобразования равно на-ибольшей допустимой разрядности двоичного числа (4т \* 5c = 20).

При делении на два могут возникнуть две ситуации в зависимости от того, делится ли без остатка число в десятичном разряде или нет. В первом случае переносов в младший разряд нет. Во втором случае возникает остаток 0,5, который при переносе в младший разряд дает число 5 или 0101 в двоичном коде.

Именно на эту величину и должно быть скорректировано содержимое младшего разряда

В табл. 2.1 приведен в качестве примера процесс преобразования десятичного числа 935 в его двоичный эквивалент.

Таблица 2.1

| T       |           | ı                    | ı                                     |                              |

|---------|-----------|----------------------|---------------------------------------|------------------------------|

| Шаг     | Операция  | Десятичная<br>запись | Эквивалент в двоично- десятичном коде | Состояние двоичного регистра |

| Исход-  | _         | 9 3 5                | 1001 0011 0101                        | 0000000000                   |

| ное со- |           |                      |                                       |                              |

| стояние | Сдвиг     | 4,5 1,5 2,5          | 0100,1 0001,1                         | 1000000000                   |

| 0a      |           |                      | 0010,1                                |                              |

| 1       | Коррекция | 4 6 7                | 0100 0110 0111                        |                              |

| 1a      | Сдвиг     | 2 3 3,5              | 0010 0011 0011,1                      | 1100000000                   |

| 2       | Коррекция | 2 3 3                | 0010 00111 0011                       |                              |

| 2a      | Сдвиг     | 1 1,5 1,5            | 0001 0001,1 0001,1                    | 1110000000                   |

| 3       | Коррекция | 116                  | 0001 0001 0110                        |                              |

| 3a      | Сдвиг     | 0,5 0,5 3            | 0000,1 0000,1 0011                    | 0111000000                   |

| 4       | Коррекция | 0 5 8                | 0000 0101 1000                        |                              |

| 4a      | Сдвиг     | 0 2,5 4              | 0000 0010,1 0100                      | 0011100000                   |

| 5       | Коррекция | 029                  | 0000 0010 1001                        |                              |

| 5a      | Сдвиг     | 0 1 4,5              | 0000 0001 0100,1                      | 1001110000                   |

| 6       | Коррекция | 0 1 4                | 0000 0001 0100                        |                              |

| 6a      | Сдвиг     | 0 0,5 2              | 0000 0000,1 0010                      | 0100111000                   |

| 7       | Коррекция | 0 0 7                | 0000 0000 0111                        |                              |

| 7a      | Сдвиг     | 0 0 3,5              | 0000 0000 0011,1                      | 1010011100                   |

| 8       | Коррекция | 0 0 3                | 0000 0000 0011                        |                              |

| 8a      | Сдвиг     | 0 0 1,5              | 0000 0000 0001,1                      | 1101001110                   |

| 9       | Коррекция | 0 0 1                | 0000 0000 0001                        |                              |

| 9a      | Сдвиг     | 0 0 0,5              | 0000 0000 0000,1                      | 1110100111                   |

| 10a     | Сдвиг     | 0 0 0                | 0000 0000 0000                        |                              |

Особенностью устройств ЧПУ является дискретный характер информации и задание траекторий в цифровом виде. Уравнения этих траекторий могут быть получены при решении разностных (а не дифференциальных) уравнении с помощью цифровых (или разностных) дифференциальных анализаторов. Между тем основы построения цифровых моделей для решения разностных уравнений и принципы построения аналоговых моделей для решения обыкновенных дифференциальных уравнений во многом схожи. Поэтому принцип проектирования интерполятора для расчета промежуточных точек некоторой запрограммированной кривой заключается в следующем.

- 1. Находим обыкновенное дифференциальное уравнение, решением которого служит уравнение воспроизводимой (заданной) траектории в непрерывной форме.

- 2. Составляем аналоговую модель (обыкновенный дифференциальный анализатор) для решения дифференциального уравнения.

- 3. По аналогии с этой моделью подбираются элементы и связи цифрового (разностного) дифференциального анализатора; оценивается точность решения в цифровом виде; уточняются параметры цифровой модели.

Имеются схемы регистров, выдающие информацию парафазным кодом, то есть информация одновременно поступает с прямых и инверсных выходов триггеров. Здесь каждый разряд регистра имеет на выходе 2 линии связи.

## 2. Содержание работы

В лабораторной работе используются тактируемые «D» — триггеры с дополнительными  $S,\,R$  входами.

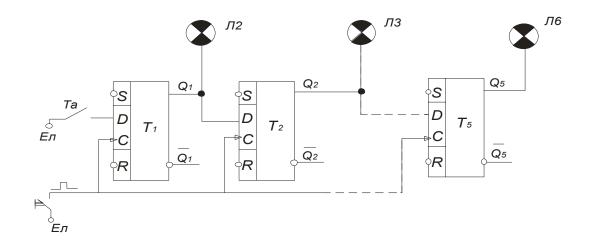

На рис. 2.1 дана функционально-логическая схема сдвигающего регистра, состоящая из пяти тактируемых «D» – триггеров.

Выход Q каждого предыдущего триггера подсоединен к входу D каждого последующего триггера. Благодаря этому тактовый импульс C устанавливает последующий триггер в состояние, в котором до

этого находился предыдущий, осуществляя тем самым сдвиг информации на разряд вправо. Вход D первого триггера служит для ввода в регистр информации в виде последовательных кодовых комбинаций, которые задаются тумблером Та. С каждым тактовым импульсом C на вход D первого триггера последовательно должны подаваться двоичные разряды вводимой информации. С выхода последнего триггера информация снимается в виде последовательных кодовых комбинаций при поступлении на регистр тактовых импульсов С и при наличии в регистре уже записанной ранее некоторой информации. При этом информация на выходе регистра появляется по отношению ко входу с задержкой на число периодов тактовых им пульсов, равное числу триггеров регистра сдвига. Вывод информации из регистра может производиться как в прямом (выход  $Q_5$  последнего триггера), так и в обратном (выход  $\bar{Q}_5$  — последнего триггера) кодах. Запись информация в регистр в виде параллельных кодовых комбинаций может быть задана с помощью входов S (установка в "1") и R (установка в "О").

Рис. 2.1. Схема сдвигающего регистра

Для нормальной работы D триггера на входы S, R необходимо подать логические единицы. Лампочки Л2, Л3, Л6 в исходном состоянии включены.

## 3. Методика выполнения работы

## 3.1. Последовательный ввод и вывод информации

- 1. Набрать на панели кассеты электрическую схему регистра сдвига, соответствующую функционально-логической схеме, приведенной на рис. 2.1.

- 2. Вход D первого триггера соединить с шиной аргумента

- 3. Вход шины С регистра тактовых импульсов подсоединить к выходу "І" кнопки генерации импульсов.

- 4. К выходам Q каждого триггера подсоединить лампочки для индикации их состояния.

Лампочка, подключенная к выходу Q последнего триггера, характеризует выходную информацию в прямом коде. Для индикации выходной информации в обратном коде необходимо подключить лампочку к выходу  $\overline{Q}_5$  последнего триггера.

- 5. Входы S и R триггеров соединить с шинами аргументов B, C соответственно и установить на шинах логическую единицу.

- 6. Установить все триггеры регистра в нуль. Для этого установить с помощью тумблера Тс на шине С логический нуль, а затем логическую единицу.

- 7. Задавая аргументу А значения логических единиц или нуля при помощи тумблера Та и, вырабатывая кнопкой генерации импульсов тактовые импульсы, последовательно ввести в регистр и вывести из регистра в прямом и обратном кодах заданную преподавателем кодовую комбинацию.

- 8. Определить необходимое число триггеров регистра для запоминания заданной кодовой комбинации и число тактовых импульсов, требующееся для ввода данной кодовой комбинации.

## 3.2. Параллельный ввод информации

- 1. Набрать на панели кассеты электрическую схему регистра, соответствующую функционально-логической схеме, приведенной на рис. 2.1

- 2. Вход шины С регистра сдвига соединить с выходом "І" кнопки генерации импульсов.

- 3. К выходам Q каждого триггера для индикации их состояния подсоединить лампочки.

- 4. Входы триггеров регистра соединить с шиной А подать на шину логическую единицу. Установить триггеры регистра в нуль. Для этого шину А перевести в состояние нуля, а затем вернуть в исходное состояние.

- 5. Подать на шину В логический нуль. Установить триггеры регистра в состояния, соответствующие заданной преподавателем кодовой комбинации. Для этого входы S триггеров, которые необходимо перевести в состояние логической единицы, соединить с шиной В.

- 6. По лампочкам установить правильность параллельного ввода информации в регистр.

- 7. Отсоединить входы R триггеров регистра сдвига от шины A. Подключить входы S триггеров регистра сдвига к шине A.

- 8. Установить триггеры регистра сдвига в единицу. Для этого шину А перевести в состояние логического нуля, а затем вернуть в исходное состояние.

- 9. Установить триггеры регистра в состояния, соответствующие заданной преподавателем кодовой комбинации. Для этого входы R триггеров, которые необходимо перевести в состояние логического нуля, соединить с шиной B.

- 10. По лампочкам установить правильность параллельного ввода информации в регистр.

# 3.3. Удвоение ранее записанного в сдвигающем регистре числа

- 1. Набрать на панели кассеты электрическую схему регистра, соответствующую функционально-логической схеме, приведенной на рис. 2.1

- 2. Вход D первого триггера соединить с шиной аргумента А.

- 3. Вход шины C тактовых импульсов подсоединить к выходу  $I^{-i}$  кнопки генерации импульсов.

- 4. К выходам Q каждого триггера для индикации их состояния подсоединить лампочки.

- 5. Входы S, R триггеров соединить с шинами аргументов В и C соответственно. Установить на шинах логическую единицу.

- 6. Установить все триггеры регистра в нуль. Для этого шину С перевести в состояние логического нуля, а затем в состояние логической единицы.

- 7. Ввести последовательно в регистр заданное преподавателем число в двоичном коде так, чтобы старший разряд кода разместился в предпоследнем триггере регистра.

- 8. По индикации лампочек убедиться, что введенное число соответствует заданному.

- 9. При помощи кнопки генерации тактовых импульсов подать один тактовый импульс. По индикации лампочек убедиться, что вновь полученное двоичное число в два раза больше ранее записанного в регистр.

- 10. Произвести умножение произвольно выбранных кодовых комбинаций на четыре и восемь.

# 4. Содержание отчета

Отчет по лабораторной работе должен содержать следующие материалы:

1. Функционально-логические схемы сдвигающих регистров последовательного и параллельного ввода и вывода информации.

- 2. Данные по числу триггеров в регистре и количеству тактовых импульсов при последовательном вводе и выводе информации.

- 3. Пояснения работы схемы умножения заданного числа на 2. Все схемы и данные должны сопровождаться краткими пояснениями.

В конце необходимо указать основные виды триггеров, их графическое обозначение и привести технические характеристики триггеров серии KI55.

## 5. Контрольные вопросы

- 1. Виды регистров.

- 2. Способы ввода информации в регистр.

- 3. Что такое «парафазный код»?

- 4. Преобразование двоично-десятичного кода в двоичный.

- 5. Какие операции обеспечивают вспомогательные схемы?

# 3. ИССЛЕДОВАНИЕ УСТРОЙСТВА ВВОДА ИНФОРМАЦИИ В ЯЧЕЙКИ БУФЕРНОЙ ПАМЯТИ СИСТЕМЫ ЧПУ

*Цель работы*. Ознакомление с функционально логическими схемами, принципом работы устройства ввода информации и ячейки буферной памяти системы ЧПУ.

#### 1. Основные положения

В функционально-логической структуре системы управления контурного устройства ЧПУ можно выделить три части, относящиеся соответственно к трем устройствам ЧПУ.

Первая часть структуры относится к устройству ввода и включает блоки считывания, усиления, формирования, контроля, дешифрации и хранения управляющей информации в буферной памяти. Вторая часть структуры относится к вычислителю и содержит блок задания скорости, интерполятор и рабочую память. Третья часть — устройство связи с исполнительными приводами подачи

(коммутаторы, блоки усиления и т.п.). Устройство ввода информации производит первичную переработку кодированной информации управляющей программы. Управляющая программа поделена на кадры, а каждый кадр представляет собой совокупность закодированных слов, которые требуют определенного преобразования перед тем, как возбудить движение исполнительных органов станка.

Преобразования эти состоят в дешифрации адресов, преобразовании кодов из двоично-десятичного в двоичный, сортировке информации по адресам, коррекции с пульта, визуализация информации в десятичном коде и др.

Устройство ввода обеспечивает покадровый ввод, хранение управляющей программы и безостановочное воспроизведение управляющей программы на станке.

В наиболее общем виде работа агрегата ввода состоит из следующих этапов.

- 1. Информация вводится построчно с помощью фотосчитывающего устройства. Введенная строка контролируется на четность. Адрес вводится в регистр адресов, дешифруется и хранится до прихода следующего адреса.

- 2. Числовая информация команд S, M, F, T, G, N вводится строка за строкой в регистр-преобразователь (одна строка в одну тетраду регистра) и, с приходом последней строки, передается в параллельном двоично-десятичном коде в соответствующие буферные регистры.

- 3. Числовая информация X, У, Z, I, J, K, L вводится в регистрпреобразователь, где организуется вычислительный цикл преобразования из двоично-десятичного кода в двоичный. Соответствующие двоичные числа передаются затем в интерполятор.

- 4. При вводе информации осуществляется контроль по структуре адреса: подсчитывается число цифровых строк и при ошибочном их числе формируется команда «Сбой».

- 5. При вводе служебной информации «Конец кадра» выдаются сигналы «Стоп» на фотосчитыватель и «Конец ввода» на интерполятор.

- 6. Фотосчитывающее устройство запускается вновь после прихода команды «Конец отработки кадра».

Устройство управления и преобразования является центральным в числе блоков, составляющих агрегат ввода. Для устройства харак-

терны два режима (режим преобразования и режим индикации), устанавливаемых триггером выбора режима. В первом режиме двоично-десятичный код геометрической информации или подачи преобразуется в двоичный код. Во втором режиме двоичный код геометрической информации переводится в десятичный код для индикации на пульте оператора.

Рассмотрим назначение отдельных блоков.

В сдвиговом регистре и комбинационном сумматоре осуществляется циклическое обращение двоичного числа с периодом в 21 строб, причем очередному стробу соответствует смещение на одни двоичный разряд. Если заблокировать в кольце (с помощью узла управления регистром) обратную связь, замыкающуюся на входе в сумматор, то за цикл, в пределах которого продолжаются сдвиги в регистре, последний будет обнулен.

Управление может быть построено так, что в регистр будет последовательно введено двоичное число из другого регистра (команда «Ввод»), или так, что за цикл обращения двоичное число в регистре будет трансформировано в дополнительный код (команда «Признак дополнительного кода», по которой на входе сумматора подключается схема преобразования в дополнительный код).

Шифратор констант последовательно опрашивается стробами параллельно с движением двоичного числа в регистре. В зависимости от числа на входе шифратора (а это число есть индекс строки 1–6), стробы «развертывают» во времени двоичный эквивалент того или иного десятичного разряда, подавая этот эквивалент последовательными двоичными разрядами на один вход сумматора как раз в те моменты времени, когда соответствующие же двоичные разряды поступают на другой вход сумматора со стороны регистра.

Таблица 3.1

| Индекс | Разрядное |      | Поступление символа "единица" |      |      |      |     |     |     |     |     |     |     |     |     |

|--------|-----------|------|-------------------------------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| строки | число     |      | на вход шифратора со стробами |      |      |      |     |     |     |     |     |     |     |     |     |

|        |           | c 14 | c 13                          | c 12 | c 11 | c 10 | c 9 | c 8 | c 7 | c 6 | c 5 | c 4 | c 3 | c 2 | c 1 |

| 6      | $10^{0}$  | 0    | 0                             | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 5      | $10^1$    | 0    | 0                             | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   |

| 4 | $10^2$          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

|---|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3 | 10 <sup>3</sup> | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| 2 | 10 <sup>4</sup> | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

Процесс «развертывания» двоичных эквивалентов десятичных разрядных чисел приведен в табл. 3.1.

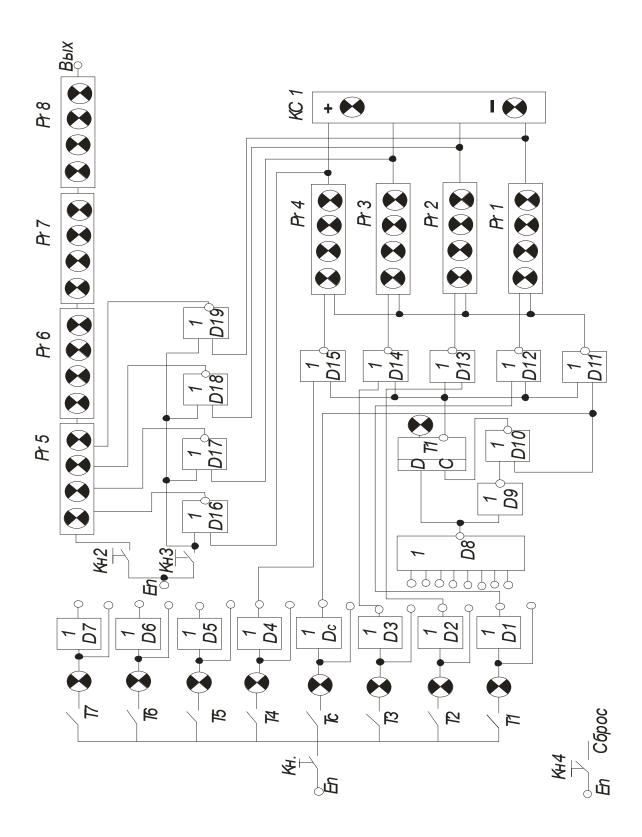

## 2. Содержание работы

В лабораторной установке (рис. 3.1) процесс считывания информации с программоносителя имитируется при помощи тумблеров ТІ...Т7 и кнопки генерации импульсов Кн.

Включение тумблеров ТІ...Т7 в соответствии с кодовой комбинацией, которую необходимо ввести в устройство ввода, с последующим нажатием кнопки Кн, обеспечивает получение сигнала, эквивалентного сигналу, получаемому при считывании информации с одной строки программы.

Тумблер  $T_c$  имитирует наличие или отсутствие сигнала. Для обеспечения процесса декодирования адресов в установке предусмотрены инверторы (D1...D7), установленные на выходе тумблеров Т1...Т7, шины прямых и инверсных сигналов по соответствующим кодовым дорожкам и дешифрирующая схема в виде логического элемента Пирса (D8).

Триггер ТІ с логическими элементами D9, D10 обеспечивает работу ячейки буферной памяти и является триггером адреса.

Для упрощения схемы лабораторной установки в ней используется четырехразрядная ячейка буферной памяти, в которую поочередно записывается геометрическая информация, набираемая тумблерами ТІ...Т4 и, следующая за тем или иным адресом. Эта ячейка собрана на элементах Пирса D11..D 15 и регистрах Pr1...Pr4.

На выходе ячейки буферной памяти установлен дешифратор знаков геометрической информации (КСІ).

Для перевода параллельного кода, поступающего в ячейку, в последовательный, имеются сдвигающие регистры Pr5...Pr8.

Элементы Шеффера D16...D19 с кнопкой Кн3 служат для поочередного считывания информации с выхода ячейки буферной памяти в сдвигающий регистр Pr5.

При замыкании кнопки Кн2 информация последовательно сдвигается из регистра Рг5 в регистр Рг6 и т.д.

## 3. Методика выполнения работы

- 1. Произвести синтез схемы дешифратора адреса, указанного преподавателем. На основании проведенного синтеза собрать на элементах D1...D7, D8 схему дешифратора.

- 2. Закодировать предложенные преподавателем символ адреса и геометрическую информацию двоичным кодом ИСО-7 бит.

- 3. При помощи тумблеров ТІ...Т7 набрать код адреса. Выключить тумблер ТС. Нажать кнопку Кн.

- 4. Если правильно был произведен синтез дешифратора адреса и схемы дешифратора была собрана без ошибок, то после отпускания кнопки Кн должна загореться лампочка у триггера ТІ, сигнализирующая о том, что триггер перешел в состояние логической "1", и разрешен ввод геометрической информации в регистры Рг1...Рг4 ячеек памяти.

- 5. Ввести в регистры Pr1...Pr4 ячеек буферной памяти предложенную преподавателем геометрическую информацию вида  $\pm$  365. При помощи тумблеров TI...T4 набрать требуемый код и ввести его в ячейку буферной памяти нажатием кнопки Kh. Ввод информации осуществлять начиная со знака и старших разрядов.

- 6. Перевести параллельный код, поступивший в ячейку буферной памяти (Рг1...Рг4) в последовательный (Рг5...Рг8).

Для этого необходимо нажать кнопку Кн3. Информация с выхода ячейки памяти через элементы D16...D19 поступит в регистр Pг5. С помощью кнопки Кн2 информацию из регистра Pг5 перевести в регистр Pг6.

Рис. 3.1. Устройство ввода информации в ячейки буферной памяти

Тумблерами ТІ...Т4 набрать новую геометрическую информацию и кнопкой Кн. ввести ее в младшие разряды Рг1...Рг4.

С выхода ячейки памяти информацию переписать кнопкой КнЗ в регистр Рг5.

Кнопкой Кн2 информацию из регистров Рг5, Рг6 переписать в регистры Рг7, Рг8.

Таким образом, информация в параллельном коде из регистров (Pr1...Pr4) будет переведена в регистры Pr5...Pr8 в последовательном коде. С выхода регистра Pr8 информация последовательно выводится из ячейки буферной памяти с помощью кнопки Kн2.

## 4. Содержание отчета

Отчет должен содержать следующие материалы:

- 1. Функционально-логическую схему устройства ввода информации в ячейки памяти.

- 2. Синтез схемы дешифратора адреса.

- 3. Краткое описание работы схемы в режиме ввода и вывода геометрической информации.

## 5. Контрольные вопросы

- 1. Способы контроля вводимой информации.

- 2. Преобразование двоично-десятичного кода в двоичный.

- 3. Основные этапы работы устройства ввода.

# 4. ИССЛЕДОВАНИЕ БЛОКА ЗАДАНИЯ СКОРОСТИ (БЗС)

*Цель работы*. Ознакомление с функционально-логической схемой и принципом работы блока задания скорости системы ЧПУ.

#### 1. Основные положения

БЗС служит для задания скорости подачи режущего инструмента посредством тактирования работы интерполятора. Скорость подачи, так же как и величина перемещений, задается определенным способом в программе. Эта программа вводится в интерполирующее устройство, где осуществляется преобразование перемещений в распределенную последовательность импульсов, причем число импульсов соответствует величинам перемещений, а частота их следования - заданной скорости подачи. В типовых интерполяторах для получения определенной контурной скорости подачи подсчитываете величина участка интерполяции:

$$\Delta S = \sqrt{\Delta X^2 + \Delta Y^2} ,$$

где  $\Delta X$  и  $\Delta Y$  перемещения по координатам X и Y.

Затем определяется время обработки данного участка интерполяции

$$\Delta t = \frac{\Delta S}{V_{KOHM}}$$

,

где  $V_{\text{конт}}$  – контурная скорость подачи.

Что позволяет определить (при данной цене одного импульса) частоту следования импульсов из блока задания скорости на вход блока декад. Такая схема применяется для интерполяторов, построенных на двоичных импульсных умножителях.

Код скорости задается четырьмя десятичными разрядами А1, А2, А3, А4.

В буферном и рабочем регистрах скорости хранится значение скорости подачи: в буферном регистре — значение скорости для отработки следующего кадра программы, в рабочем регистре — зна-

чение скорости подачи в текущий момент времени. В данной работе рассматривается только режим равномерной подачи, т.е. значения разрядов

A1, A2, A3, где A1 – признак торможения в конце отработки кадра;

А2 – порядок скорости подачи в условной форме;

А3 – мантисса скорости подачи.

Рассмотрим функциональную структуру блока задания скорости, который вместе с интерполятором входит в состав агрегата «вычислитель». В круг задач блока задания скорости входят: передача в интерполятор последовательности импульсов заданной частоты; поддержание постоянной контурной скорости отработки; осуществление разгона и торможения с автоматическим определением участка пути торможения.

Адресу F сопутствуют в программе пять символов числовой информации. Старшим разрядом задаются режимы скорости: «Разгон», «Торможение», «Быстрый ход». Остальными разрядами задается величина подачи (непосредственно в миллиметрах в минуту). Информация о режимах поступает из регистра числа в буферный регистр режимов подачи

Информация о величине подачи поступает из регистрапреобразователя последовательным двоичным кодом и записывается в буферном регистре. В режиме «Ускоренная отработка» информация о величине рабочей подачи блокируется и обеспечивается некоторая постоянная ускоренная подача, на которой ведется холостая отладка программы. В начале кадра информация переписывается из буферных регистров в рабочий регистр режимов подачи и регистр F величины подачи.

Для формирования необходимой частоты выходного сигнала используется регистр-накопитель в котором за один вычислительный период, задаваемый циклом стробов, к его предыдущему значению прибавляется число, представляющее собой код скорости.

Разрешение на суммирование обеспечивает синхронизованный сигнал генератора. В силу того, что разрядная сетка регистранакопителя ограничена, на его выходе возникают импульсы переполнения, частота которых пропорциональна коду скорости и ча-

стоте генератора. Выход импульсов переполнения представляет собой команду «Строб-шаг», по которой интерполятором выдаются импульсы управления к приводу подачи x, приводу подачи z или обоим приводам одновременно.

Для поддержания постоянной контурной скорости в регистрнакопитель вводится (после каждого цикла переполнения) некоторое дополнительное число, величина которого зависит от того,

каковой была предыдущая управляющая команда. Это позволяет

целенаправленно изменять частоту переполнения, т. е. частоту

строб-шагов. Блок поддержания постоянной контурной скорости

содержит узел формирования и дешифрации коэффициентов и узел

выработки добавочных чисел.

Из-за того, что отработка ведется с шагом по одной или двум координатам одновременно, мгновенная скорость подачи непрерывно изменяется. Об угле наклона текущего профиля можно судить по числу шагов, отработанных в одно и то же время. Для подсчета шагов по каждой координате применены счетчики до двух Сч2, в зависимости от состояния которых вырабатывается определенный коэффициент (табл. 4.1).

Таблица 4.1

| Угол наклона | Состояние<br>Сч2 для х | Состояние<br>Сч2 для z | Коэффициент |

|--------------|------------------------|------------------------|-------------|

| 0            | 2                      | 0                      | 1           |

| 45           | 2                      | 1                      | 0,707       |

| 63,30        | 2                      | 2                      | 0,447       |

| 76           | 1                      | 2                      | 0,5         |

| 90           | 0                      | 2                      | 0,5         |

Режим разгона и торможения обеспечивается генератором управляемой частоты. Появление единичного сигнала на входе управления генератором означает начало режима торможения, а наличие нулевого сигнала равнозначно режиму разгона (оба переходных режима возможны только при наличии соответствующих разрешающих команд со стороны блока режимов).

От блока задания скорости, управляющие команды в унитарном коде отправляются в координатные приводы. Таким образом, блок

задания скорости обеспечивает отработку перемещений с заданной скоростью подачи. Другими функциями блока задания скорости являются: разгон в начале отработки кадра, торможение на стыке кадров при смене скорости подачи, автоматическое поддержание постоянной контурной скорости при мгновенных включениях в работу одной, двух или трех координат.

Все вычислительные и другие циклы в устройстве ЧПУ синхронизированы генератором тактов (всего четыре такта) и стробов (всего пять стробов). Число тактов и стробов обусловлено последовательно-параллельным характером передачи информации в регистрах памяти.

При управлении приводами кодом скорости сигналы ступеней скорости управляют в блоке подач выдачей на шины системы установок скоростей. Полученный код скорости подачи выдается с выходных шин сумматора, запоминается в регистрах блока подач и через блок усилителей выдается на внешние разъемы.

Управление главным приводом осуществляется выдачей из памяти блока главного привода, через блок усилителей, на выходные разъемы системы управления, сигналов включения механических ступеней скорости и кода электрических ступеней внутри механических диапазонов.

Код вспомогательных команд М выдается на выход устройства с памяти блока адресов через блок усилителей.

Узел датчиков преобразует в код информацию о положении исполнительных механизмов ТО относительно начала отсчета и обеспечивает питание датчиков.

Таким образом, БЗС обеспечивает отработку перемещений с заданной скоростью подачи. Другими функциями БЗС являются: разгон в начале отработки кадра, торможение на стыке кадров при смене скорости подачи, автоматическое поддержание постоянной контурной скорости.

Все вычислительные и другие циклы в устройстве ЧПУ синхронизированы генератором тактов (всего 4 такта) и стробов (всего 5 стробов).

Импульс опроса выходного блока поступает в соответствующий момент времени от БЗС; управляющие команды в унитарном коде

отправляются в координатные приводы: блокировка интерполятора снимается до очередной команды.

Если период (тах коэффициент деления) БЗС равен числу отсчетов за один оборот датчика, то код подачи, занесенный в БЗС с учетом цены отсчета ТО будет прямо соответствовать подаче мм/оборот.

Если тах коэффициент деления равен, например, 4096, датчик за один оборот выдает 4096 импульсов, цена отсчета ТО 0,001мм и задан код подачи F = 200, то на выходе БЗС за каждый оборот датчика будет 200 импульсов, что соответствует подаче 0,2 мм/оборот.

## 2. Содержание работы

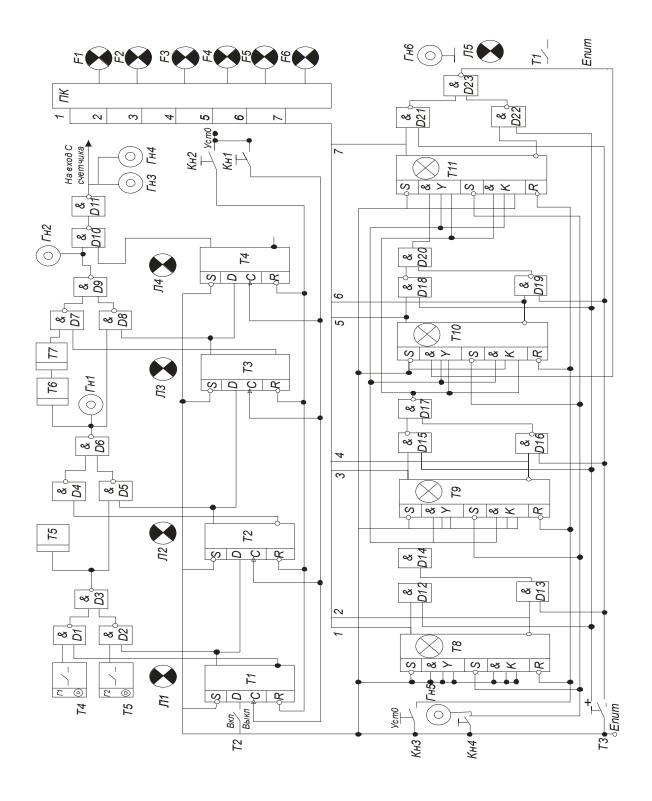

Блок задании скорости состоит из 2-х генераторов Г1 и Г2, кодовых триггеров ТI, Т2, Т3, Т4, делителя частоты Т5, Тб, Т7 и управляющих элементов, собранных на логических элементах D1...D11 (см рис. 4.1). Логические элементы D10, D11 обеспечивают прохождение сигнала на выход Б3С лишь при нахождении триггера Т4 в состоянии логической единицы.

Триггер ТІ служит для выбора одного из 2-х генераторов  $\Gamma$ 1 или  $\Gamma$ 2. С помощью триггеров  $\Gamma$ 2,  $\Gamma$ 3 выбирается один из трех коэффициентов деления 2,4.8.

Например, для задания выходного сигнала БЗС с  $f \sim 100~\Gamma$ ц при частоте следования импульсов первого генератора  $800~\Gamma$ ц необходимо на кодовые триггеры подать двоичный код 0001.

Тумблер Т2 и кнопка Кн1 предназначены для ручного ввода в кодовые триггеры требуемого кода управления.

Для установки триггеров ТІ...Т4 в исходное положение используется кнопка Уст"0". Состояния триггеров ТІ...Т4 контролируются с помощью лампочек Л1...Л4.

Рис. 4.1. Блок задания скорости и электронный коммутатор

# 3. Методика проведения работы

- 1. Включить генераторы Г1 и Г2 с помощью тумблера Т4 и Т5. При помощи частотомера или осциллографа определить частоты следования импульсов с генераторов.

- 2. На основании функционально-логической схемы БЗС и измеренных частот генераторов заполнить таблицу 4.1 возможных скоростей подач и им соответствующих кодов управления в двоичных и десятичных системах счисления.

#### Таблица 4.1

| Скорость<br>подачи, мм/с | Двоичный код<br>управления | Десятичный<br>код управле-<br>ния | Количество<br>импульсов |

|--------------------------|----------------------------|-----------------------------------|-------------------------|

|                          |                            |                                   |                         |

- 3. Закодировать заданную преподавателем скорость подачи в двоичном коде. Установить триггеры БЗС в нуль кнопкой Кн2.

- 4. Ввести в БЗС полученный двоичный код с помощью тумблеров Т2 и кнопки Кн.

- 5. Подключить к гнездам Гн3, Гн4 частотомер или осциллограф и определить соответствие между заданной и действительной скоростью подачи.

- 6. Выставить кодовые триггеры на ноль и поочередно, вводя коды, обеспечивающие все возможные скорости подачи, проверить соответствие их, вычисленным аналитически.

## 4. Содержание отчета

Отчет по лабораторной работе должен содержать следующие материалы:

- 1. Функционально-логическую схему БЗС.

- 2. Таблицу скоростей подач с соответствующими им кодами управления.

- 3. Основные выводы по лабораторной работе.

Все таблицы, схемы и расчеты должны сопровождаться краткими пояснениями.

## 5. Контрольные вопросы

- 1. Для чего используется БЗС?

- 2. Где содержится информация о скорости подачи в конкретный момент времени?

- 3. Что необходимо сделать, чтобы коэффициент деления был 32?

- 4. В какие блоки СЧПУ поступают импульсы после БЗС?

## 5. ИССЛЕДОВАНИЕ ЭЛЕКТРОННОГО КОММУТАТОРА ШАГОВОГО ПРИВОДА ПОДАЧИ

*Цель работы*. Ознакомление с функционально-логической схемой, принципом работы электронного коммутатора шагового привода подачи.

## 1. Основные сведения

Электронный коммутатор (ЭК) предназначен для преобразования последовательности входных импульсов в команды для последовательного включения фаз шагового двигателя, Коммутаторы строятся по 3-х, 6-и, 12-и и более сложным схемам коммутации. Шеститактная схема коммутации применяется для управления шаговым двигателем ШД-4. Цикл работы ЭК заканчивается по приходу шестого импульса. Двенадцатитактная схема коммутации применяется для управления ШД с шестью выводами обмоток (типа ШД-5Д1).

Основное требование к ЭК – обеспечение заданного закона распределения импульсов при минимально возможном количестве входящих в него элементов.

Число выходных сигналов определяется количеством фаз ШД. Последовательность переключения каналов коммутатора выбирают, учитывая получение требуемого статического момента ШД и нужного шага.

Коммутаторы бывают реверсивными и нереверсивными. Реверсивные — управляются по двум входным каналам. Реверс производится изменением последовательности переключения обмоток ШД и соответственно ячеек коммутатора. Импульсы программы поступают по двум управляющим входам, обеспечивающим прямой и обратный порядок последовательности включения обмоток ШД.

Коммутатор может быть построен в виде:

- счетчика с дешифратором и сумматором, обеспечивающим требуемую схему коммутации;

- сдвигающего регистра;

- реверсивного счетного кольца.

В процессе коммутации фаз вектор магнитного поля непрерывно поворачивается с угловой скоростью, соответствующей частоте поступающих на коммутатор импульсов управления.

Импульсы с электронного коммутатора усиливаются по мощности и через узел резисторов для повышения быстродействия ШД поступают на его обмотки.

Электронный коммутатор представляет собой кольцевой сдвиговый регистр, изменяющий свое состояние под действием каждого очередного входного импульса; смена состояний коммутатора приводит (через усилитель мощности) к переключению фаз ШД и повороту его ротора на угловой шаг. Цена шага неизменна и обусловлена особенностями конструкции ШД. ШД — это своеобразная гидрокопировальная система с жесткой ОС, выполняющая копирование с усилением крутящего момента. Таким образом, шаговые перемещения воспроизводятся с усилением на общем силовом входе привода.

Возможны различные законы коммутации с различной цикличностью. Чем больше фаз включено одновременно, тем выше крутя-

щий момент, развиваемый ШД. В процессе коммутации фаз вектор магнитного поля непрерывно поворачивается с угловой скоростью, соответствующей частоте поступающих импульсов управления. Ротор отстает от этого вектора, что и создает «натяг» в магнитном поле. Чем выше частота управления, тем выше нагрузка, приложенная к ротору, тем больше отставание. Это отставание не должно превышать цикл (12) коммутации т.к. это приведет к нарушению синхронизации и потере информации. Частота приемистости — мгновенный перепад частоты управления, отрабатываемый ШД без потери синхронизации. Другое ограничение называется максимальной частотой управления, которая допустима для ШД в режиме разгона. Поэтому для ШД частота приемистости лежит в районе до 2000 Гц, а максимальная частота достигает 16—18кГц.

## 2. Содержание работы

Электронный коммутатор построен по двенадцатитактной схеме коммутации и применяется для управления шаговыми двигателями с шестью выводами обмоток (типа ШД-5Д1). Цикл работы таких схем заканчивается по приходу двенадцатого импульса.

Коммутатор состоит из реверсивного счетчика по модулю 12, собранного на триггерах Т8...Т11, элементов Д12...Д23 и преобразователя кодов ПК (рис. 4.1 лабораторной работы №4).

Коммутатор может изменять порядок распределения импульсов по фазам. Прямое и обратное распределение импульсов обеспечивает вращение ротора шагового двигателя в различных направлениях.

Выбор вида распределения импульсов по фазам осуществляется с помощью тумблера ТЗ. Кнопка Кн4 "РУ" вырабатывает импульсы, поступающие на вход реверсивного счетчика. Состояние триггеров реверсивного счетчика индицируется с помощью лампочек. Кнопка Кн3 "Уст 0" используется для установки в нуль триггеров счетчика.

Преобразователь кодов осуществляет преобразование кода, описывающего состояние счетчика в код, характеризующий состояние фаз шагового двигателя. Состояние фаз F1–F6 шагового двигателя индицируется с помощью лампочек.

## 3. Методика выполнения работы

- 1. Установить триггеры реверсивного счетчика е нуль с помощью Кн3 "Уст 0". Проконтролировать загорание лампочек, индицирующих состояние фаз F1, F6. Установить прямое распре деление импульсов электронного коммутатора по фазам ШД, для этого тумблер Т3 перевести в положение "+".

- 2. Нажатием кнопки Кн4 "РУ" перевести счетчик в состояние 0001. Проконтролировать по лампочкам состояние фаз F1, F2, F3.

- 3. С помощью кнопки Кн4 имитировать поступление на вход реверсивного счетчика входных импульсов, наблюдая прямое распределение фаз шагового двигателя.

- 4. Установить триггеры реверсивного счетчика в нуль с помощью кнопки КнЗ "Уст0". Проконтролировать загорание лампочек, индицирующих состояние фаз F1, F2. Установить обратное распределение импульсов коммутатора по фазам ШД. Дл этого тумблер ТЗ перевести в положение "-".

- 5. Нажатием кнопки Кн4 "РУ" перевести счетчик в состояние 1011.

Проконтролировать по лампочкам состояние фаз F1, F2, F6.

- 6. С помощью кнопки Кн4 имитировать поступление на вход реверсивного счетчика иупульсов, контролируя при этом обратное распределение фаз шагового двигателя.

- 7. Подключить блок задания скорости. Ввести в БЗС двоичный код, соответствующий заданной преподавателем скорости подач.

- 8.Включить генераторы Г1 и Г2 Б3С. Тумблером Т3 подавать направление коммутации "+" или "-" и проконтролировать прямое и обратное распределение фаз в автоматическом режиме.

- 9.Задавая возможные значения кодов скоростей подач проконтролировать работу коммутатора в автоматическом режиме.

# 4. Содержание отчета

Отчет по лабораторной работе должен содержать следующие материалы:

1. Функционально-логическую схему электронного коммутатора.

- 2. Таблицу распределения импульсов по фазам при прямом и обратном направлении коммутации.

- 3. Основные выводы по лабораторной работе. Все таблицы, схемы и расчеты должны сопровождаться кратким пояснением.

## 5. Контрольные вопросы

- 1. Какие схемы коммутации применяются в системах управления станками с ЧПУ?

- 2. Как формируется первоначальная информация о направлении вращения ШД?

- 3. Что такое частота «наброса» для ШД и ее значение для ШД-5Д1?

#### 6. СИНТЕЗ ЛИНЕЙНОГО ИНТЕРПОЛЯТОРА

*Цель работы*. Ознакомление с функционально-логической схемой, принципом действия и основными характеристиками линейного интерполятора.

#### 1. Основные положения

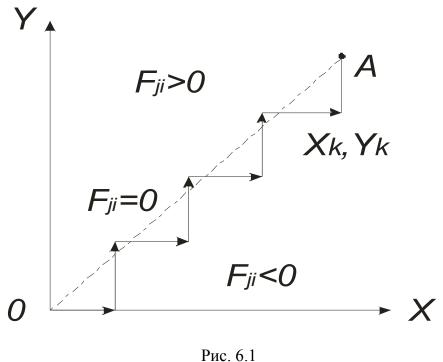

Работа линейного интерполятора заключается в выработке признака перемещения режущего инструмента по той или иной координате в зависимости от знака оценочной функции в промежуточной точке траектории, вычислении координат точки, в которую сделан шаг, и в вычислении величины оценочной функции в этой точке.

Кроме того, интерполятор определяет окончание процесса интерполяции, сравнивая значения координат промежуточных и конечных точек. Интерполируемая прямая OA рис. 6.1 делит плоскость XУ на две области: область, где оценочная функция F>0, находится над прямой; область, где F<0, расположена под прямой и  $F\neq 0$  для точек, расположенных на прямой линии.

РИС. О.1

Если промежуточная функция траектории находится в области F>0, то следующий шаг производится по оси X, если же в области F<0, то шаг по оси Y. Значения оценочной функции для промежуточных точек траектории можно определить по формуле

$$F_{ij} = YX_k - XY_k,$$

где  $X_{k}Y_{k}$  – координаты конечной точки обработки;

$X_iY_i$  – координаты текущих точек обработки

$$(i = 0,1,2,3...)$$

$j = 0,1,2,3...)$

Если координаты задаются числом шагов, то текущие координаты точки обработки при шаге по осям координат увеличиваются на единицу:

$$X_{i+1} = X_i + 1$$

$Y_{y+1} = Y_j + 1$ .

Текущее значение оценочной функции с каждым шагом по любой из осей координат изменяется следующим образом:

при шаге по оси X:  $F_{i+1,j} = F_{i,j} - Y_k$

при шаге по оси Y:  $F_{i,j+1} = F_{i,j} + X_k$

Начальное значение величины оценочной функции  $F_{co}=0$  и, следовательно, первый шаг всегда делается по оси X. Для каждой промежуточной точки траектории интерполяции величина оценочной функции зависит от координат конечной точки интерполируемого отрезка  $X_k$  и  $Y_k$ , вводимых из программы. Входная информация на блок интерполяции поступает с запоминающего блока. Выходная информация интерполятора обычно представлена в импульсной форме, т.е. в виде последовательности импульсов по каждой координате, частота которых определяет скорость подачи, а общее количество — пройденный путь по данной координате. Максимальная частота импульсов на выходе интерполятора является одной из самых основных его характеристик и в современных СЧПУ имеет величину 5–10 Кгц.

Особенностью устройств ЧПУ является дискретный характер информации и задание траекторий в цифровом виде.

Уравнения этих траекторий могут быть получены при решении разностных (а не дифференциальных) уравнении с помощью цифровых (или разностных) дифференциальных анализаторов.

Между тем основы построения цифровых моделей для решения разностных уравнений и принципы построения аналоговых моделей для решения обыкновенных дифференциальных уравнений во многом схожи.

Поэтому принцип проектирования интерполятора для расчета промежуточных точек некоторой запрограммированной кривой заключается в следующем.

- 1. Находим обыкновенное дифференциальное уравнение, решением которого служит уравнение воспроизводимой (заданной) траектории в непрерывной форме.

- 2. Составляем аналоговую модель (обыкновенный дифференциальный анализатор) для решения дифференциального уравнения.

- 3. По аналогии с этой моделью подбираются элементы и связи цифрового (разностного) дифференциального анализатора; оценивается точность решения в цифровом виде; уточняются параметры цифровой модели.

## 2. Описание установки

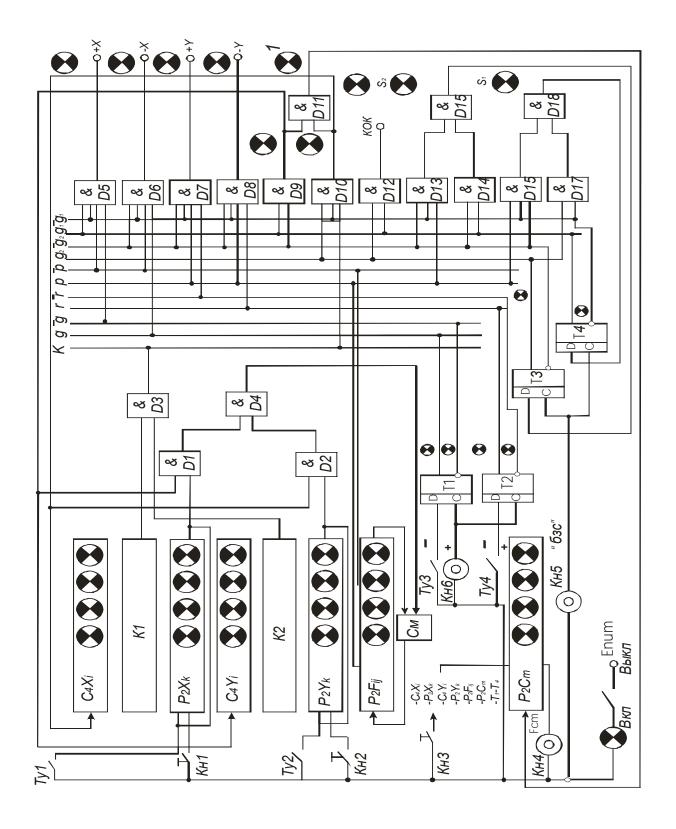

Функционально-логическая схема линейного интерполятора состоит из счетчиков текущих значений координат  $X_i, Y_j(C_4x_i \ u \ C_4y_k)$ , сдвигающих регистров конечных значений координат  $X_k, Y_k(P_rx_k \ u \ P_ry_k)$ , сдвигающего регистра хранения текущего значения оценочной функции  $F_{ij}(P_rF_{ij})$ , сдвигающего регистра генерации стробов  $P_rC_T$ , сумматора  $(C_m)$ , триггеров хранения знаков конечных значений координат  $(T_1, T_2)$ , триггеров управления  $(T_1 - T_4)$  и элементов управления D5...D18, формирующих выходные функции (рис. 6.2).

Выходные сигналы с интерполятора индицируются светодиодами  $\pm X, \pm Y$ , подключенными к выходам элементов D5...D8. Элемент D12 вырабатывает сигнал, характеризующий конец обработки кадра КОК.

При подаче сигнала с интерполятора на очередной шаг перемещения режущего инструмента по соответствующей координате одновременно сигнал поступает на соответствующий счетчик текущего значения координаты. С элементов D9, D10 снимаются сигналы, обеспечивающие вычисление текущего значения оценочной функции. Для вычисления значения оценочной функции служит сумматор. На вход сумматора сигналы поступают со сдвигающего регистра текущего значения оценочной функции  $(P_rF_{ii})$  и с одного регистров конечного сдвигающих значения координат  $(P_r x_{\kappa}, P_r y_k)$  . При очередном вычислении оценочной функции  $F_{xi}$ конечные значения координат  $X_{\scriptscriptstyle k}$  и  $Y_{\scriptscriptstyle k}$  одновременно с подачей на сумматор переписывается в собственные сдвигающие регистры. Стробирование схемы интерполятора осуществляет регистр стробов, на вход которого с элемента D11 поступает сигнал "І". При появлении сигнала I на выходе регистра стробов образуется столько стробирующих импульсов, сколько необходимо для обеспечения функции текущего значения оценочной Элементы расчета

D13...D15, D16...D18 служат для выработки функций возбуждения  $S_1$ ,  $S_2$ . Комбинационные схемы КІ и К2 обеспечивают сравнение кодов и вырабатывают сигнал равенства текущих значений координат  $X_i$  и  $Y_j$  с конечными значениями тех же координат  $(X_k, j_k)$ . Тумблеры Туl, Ту2 и кнопки Кн1, Кн2 предназначены для ручного ввода в сдвигающие регистры конечных значений координат  $X_k$  и

$Y_k$  заданных кодов. Тумблеры Ту3 и Ту4 и кнопка Кн6 обеспечивают ввод кодов, характеризующих знаки конечных значений координат в триггеры знаков Т1 и Т2. Кнопка Кн5 «бзс» имитирует импульсы, поступающие с блока задания скорости, кнопка Кн4 "Fcm" вырабатывает импульсы, поступающие на сдвиговый регистр стробов и обеспечивающие стробирование схемы интерполятора.

Кнопка Кн3 «Сброс» служит для установки в нуль сдвигающих регистров конечных значений координат, сдвигающего регистра оценочной функции, счетчиков текущих значений координат, регистра стробов, триггеров координат управления и элементов памяти сумматора.

Подача напряжения +5В в электрическую схему интерполятора осуществляется с помощью тумблера Епит.

## 3. Методика выполнения работы

- 1. Включить тумблер Е пит. Установить все счетчики, сдвигающие регистры и триггеры в нуль при помощи кнопки Кн3 "Сброс"

- 2. Тумблерами Туl, Ту2 и кнопками Кн1, Кн2 ввести в сдвигающие регистры конечные значения координат (заданные преподавателем кодовые комбинации).

- 3. При помощи тумблеров Ту3, Ту4 и кнопки Кн6 ввести коды знаков конечных значений координат в триггеры знаков

- 4. Проконтролировать загорание одного из светодиодов  $\pm X, \pm Y$ , сигнализирующих о выбранном направлении перемещения режущего инструмента.

Рис. 6.2. Схема линейного интерполятора

- 5. Выполнить шаг вдоль выбранного направления перемещения. Для этого необходимо нажать кнопку Кн5 "БЗС". Проконтролировать занесение единицы в счетчик текущего значения координаты, по которой был выполнен шаг.

- 6. При возникновении сигнала «1» на элементе D11 необходимо нажатием кнопки Kн4 "Fcm" обеспечить выработку стробов для расчета текущего значения оценочной функции  $F_{ij}$ . Загорание всех светодиодов регистра стробов сигнализирует о выполнении расчета текущего значения  $F_{ij}$ . Значение оценочной функции, представленной в дополнительном коде, индицируется с помощью светодиодов.

- 7. Нажатием кнопки Кн5 "бзс" проверить появление сигнала КОК, который сигнализирует об окончании процесса интерполяции. При отсутствии сигнала КОК выбрать направление перемещения инструмента на следующем шаге нажатием кнопки Кн5. Повторить операции по пунктам 5,6,7. Управление схемой интерполятора производить до момента появления сигнала КОК.

## 4. Содержание отчета

Отчет по лабораторной работе должен содержать следующие материалы:

- 1. Описание принципа работы линейного интерполятора.

- 2. Функционально-логическую схему интерполятора.

- 3. Граф-схему алгоритма линейного интерполятора.

- 4. Расчеты, связанные с определением количества стробов и частоты следования импульсов с блока задания скорости (по заданной рабочей скорости инструмента).

## 5. Контрольные вопросы

- 1. Какие существуют методы интерполяции применительно к станкам с ЧПУ?

- 2. Назовите недостатки при использовании линейного интерполятора для обработки деталей с фасонным контуром.

- 3. В чем суть линейной аппроксимации и когда она применяется?

- 4. Какие дискретные автоматы использованы при построении данной схемы интерполятора?

## СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

- 1. Программное управление станками. М. : Машиностроение, 1981. С. 398.

- 2. Серебреницкий, П. П. Программирование для автоматизированного оборудования / П. П. Серебреницкий, А. Т. Схиртладзе. М.: Высшая школа, 2005. 350 с.

- 3. Денисенко, В. В. Компьютерное управление технологическим процессом, экспериментом, оборудованием / В. В. Денисенко. М. : Горячая линия-Телеком, 2009. 608 с.

- 4. Готшальк, О. А. Программное управление оборудованием / О. А. Готшальк. Л. : СЗПИ, 1980. 68 с.

- 5. Шишмарев, В. Ю. Автоматизация технологических процессов / В. Ю. Шишмарев. М. : Академия, 2005. 352 с.

# СОДЕРЖАНИЕ

| 1. | СТРУКТУРНЫЙ СИНТЕЗ ДИСКРЕТНЫХ АВТОМАТОВ                                       | 3  |

|----|-------------------------------------------------------------------------------|----|

| 2. | ИССЛЕДОВАНИЕ СДВИГАЮЩИХ РЕГИСТРОВ                                             | 10 |

| 3. | ИССЛЕДОВАНИЕ УСТРОЙСТВА ВВОДА ИНФОРМАЦИИ В ЯЧЕЙКИ БУФЕРНОЙ ПАМЯТИ СИСТЕМЫ ЧПУ | 18 |

| 4. | ИССЛЕДОВАНИЕ БЛОКА ЗАДАНИЯ СКОРОСТИ (БЗС)                                     | 25 |

| 5. | ИССЛЕДОВАНИЕ ЭЛЕКТРОННОГО КОММУТАТОРА<br>ШАГОВОГО ПРИВОДА ПОДАЧ               | 32 |

| 6. | СИНТЕЗ ЛИНЕЙНОГО ИНТЕРПОЛЯТОРА                                                | 36 |

| 7. | СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ                                              | 43 |

#### Учебное издание

#### **КАПУСТИНА** Анна Михайловна **СИРОТИН** Феликс Львович

## СИСТЕМЫ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ

Методическое пособие по лабораторным и практическим работам для студентов специальностей 1-53 01 01 «Автоматизация технологических процессов и производств», 1-53 01 06 «Промышленные роботы и робототехнические комплексы»

Технический редактор О. В. Песенько

Подписано в печать 11.12.2013. Формат  $60\times84^1/_{16}$ . Бумага офсетная. Ризография. Усл. печ. л. 2,61. Уч.-изд. л. 2,04. Тираж 100. Заказ 355.

Издатель и полиграфическое исполнение: Белорусский национальный технический университет. ЛИ № 02330/0494349 от 16.03.2009. Пр. Независимости, 65. 220013, г. Минск.