# РОССИЙСКОЕ АГЕНТСТВО ПО ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ

### (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

(21), (22) Заявка: 4491963/09, 10.10.1988

(46) Опубликовано: 20.03.1997

(56) Список документов, цитированных в отчете о поиске: Гольденберг Л.М., Теория и расчет импульсных устройств на полупроводниковых приборах, М.: Связь, 1969. с. 524-529.

(71) Заявитель(и): Белорусская государственная политехническая академия (BY)

(72) Автор(ы): Сычик Василий Андреевич[ВҮ], Хачатрян Юрий Михайлович[ВҮ], Шабуневский Константин Константинович[ВҮ]

(73) Патентообладатель(ли): Белорусская государственная политехническая академия (BY) J

20

S

$\infty$

ത

റ

#### (54) ЭЛЕМЕНТ ПАМЯТИ

(57) Реферат:

Использование: в вычислительной технике, для построения репрограммирующих запоминающих устройств. Сущность изобретения: элемент памяти содержит полупроводниковое основание в виде монокристаллического слоя либо поликристаллического пленочного слоя, спаренные биполярные транзисторы с металлизацией, разделенные слоями изоляции, выводы записи, считывания, стирания и выводы источника питания. Пары биполярных структур размещены на торцовых сторонах полупроводникового основания,

а по его длине последовательно расположены изоляционный слой и слой ферромагнитного материала, содержащий два полюсных наконечника. Биполярные транзисторы в парах соединены последовательно, эмиттеры нижних биполярных транзисторов пар соединены с корпусом, коллекторы верхних транзисторов пар соединены с источником питания, а базы верхних транзисторов каждой из пар посредством резисторов подключены к базам транзисторов смежных пар. 2 ил.

5

J 2075786

## (19) **RU**(11) **2 075 786**(13) **C1**

#### RUSSIAN AGENCY FOR PATENTS AND TRADEMARKS

### (12) ABSTRACT OF INVENTION

(21), (22) Application: 4491963/09, 10.10.1988

(46) Date of publication: 20.03.1997

(71) Applicant(s):Belorusskaja gosudarstvennaja politekhnicheskaja akademija (BY)

(72) Inventor(s): Sychik Vasilij Andreevich[BY], Khachatrjan Jurij Mikhajlovich[BY], Shabunevskij Konstantin Konstantinovich[BY]

J

20

S

7

$\infty$

တ

(73) Proprietor(s):Belorusskaja gosudarstvennaja politekhnicheskaja akademija (BY)

#### (54) MEMORY GATE

(57) Abstract:

FIELD: computer engineering. SUBSTANCE: device has semiconductor substrate which is designed as single- crystal or polycrystal film layer, joined bipolar transistors with wiring. Said transistors are separated insulation layers. ln addition device terminals for writing, reading, clearing terminals of power supply unit. Pairs of bipolar structures are located on ends of semiconductor substrate; while insulation layer and layer of ferromagnetic material are located along semiconductor substrate. Layer of ferromagnetic material has flat pole two pieces. Bipolar transistors in pairs are connected in series, emitters of lower bipolar transistors in pairs are connected to power supply, bases of upper

transistors in each pair are connected to bases of lower transistors of adjacent pairs. EFFECT: increased functional capabilities. 2 dwg

Страница: 3

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении репрограммирующих запоминающих устройств.

5

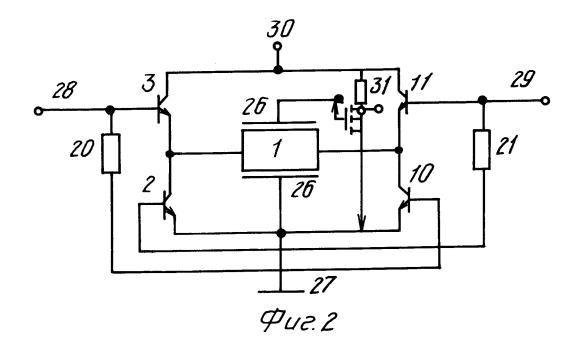

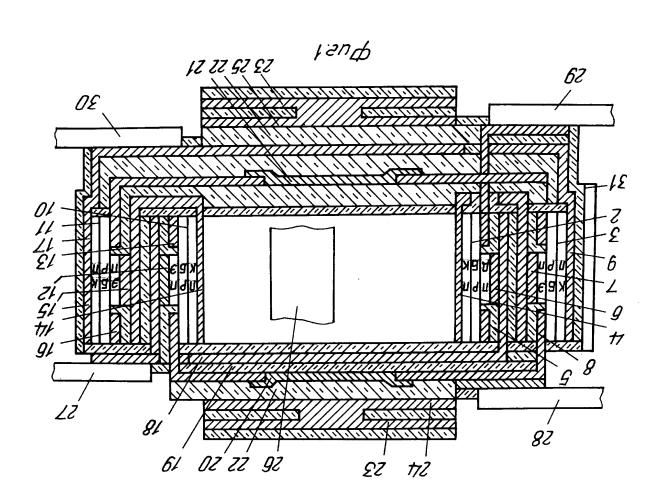

На фиг. 1 изображена конструкция элемента памяти; на фиг. 2 - электрическая схема включения его структурных элементов.

Элемент памяти состоит из полупроводникового основания (подложки) 1, биполярных транзисторов 2 и 3 левой пары с омическими контактами к эмиттеру 4, базе 5, коллектору 6 транзистора 2 и к эмиттеру 7 базе 8, коллектору 9 транзистора 3, биполярных транзисторов 10 и 11 правой пары с омическими контактами к эмиттеру 12, базе 13, коллектору 14 транзистора 10 и эмиттеру 15, базе 16, коллектору 17 транзистора 11. Омические контакты 6 и 14 к коллекторам транзисторов 2 и 10 являются одновременно омическими контактами к полупроводниковому основанию 1.

В соответствии с фиг. 2 эмиттеры транзисторов 2 и 10 с помощью металлизации в виде металлических пленочных слоев 18, разделенных слоями диэлектрика 19, непосредственно соединены между собой и с корпусом, коллектор 6 транзистора 2 соединен непосредственно с эмиттером 7 транзистора 3, а эмиттер 15 транзистора 11 соединен с коллектором 14 транзистора 10. Между коллекторами транзисторов 2 и 10 включено полупроводниковое основание 1, представляющее собой диагональ моста, состоящего из биполярных транзисторов 2, 3, 1, 11. База верхнего биполярного транзистора 3 левой пары соединена посредством резистора 20 с базой нижнего транзистора 10 правой пары, а база верхнего биполярного транзистора 11 правой пары соединена посредством резистора 21 с базой нижнего биполярного транзистора 2 левой пары. По длине подложки, по ее контуру расположен изоляционный слой 22, на котором сформирован слой ферромагнитного материала 23, содержащий два полюсных наконечника 24 и 25, а на перпендикулярных к полюсным наконечникам сторонах полупроводникового основания 1 расположены электроды считывания 26, один из которых соединен с общим выводом 27.

Элемент памяти также содержит вывод записи 28, вывод стирания 29 и вывод питания 30. Если уровень записанного в элементе памяти информационного сигнала (бита) ниже допустимого для конкретного типа логики, используется усилительный элемент 31, обеспечивающий повышение уровня записанной информации до требуемого значения. Этот элемент представляет усилитель постоянного тока на полевом транзисторе, реализованный по интегральной технологии.

Левая и правая пары контактирующих с полупроводниковым основанием 1 биполярных транзисторов 2, 3 и 10, 11, их металлизации и межслойная изоляция реализованы по стандартной гибридной и твердотельной технологии со стандартной топологией, толщинами пленок, со стандартными размерами активных и пассивных элементов. Изоляционный слой 22 формируется по всей длине полупроводникового основания 1 и обладает толщиной, достаточной для электрической изоляции полюсных наконечников 24 и 25 от находящихся под напряжением токопроводящих участков металлизации.

- Оптимальная их толщина составляет 1-5 мкм. Слой ферромагнитного материала 23 выполнен из магнитотвердого материала, например типа альни, либо ферритов с прямоугольной петлей гистерезиса (никель-цинковые ферриты марки 1,5 Вт, 1,3 Вт, 2 Вт), а полюсные наконечники 24, 25 из магнитомягкого материала, например пермаллоя, магнитомягких марганец-цинковых ферритов 1500 нм, причем их толщина, как показали результаты эксперимента, составляет 5-20 мкм. Полюсные наконечники 24, 25 отделены от слоя ферромагнитного материала (магнитопровода) 23 слоем изоляции, а их контакт осуществляется в средней части для получения наибольшей магнитной индукции в средней части полупроводникового основания 1. Оптимальное соотношение длин горловины и полюсного наконечника, как показали результаты эксперимента, составляет (1:2)-(1:10).

- Размеры полупроводникового основания 1 зависят от типа материала полупроводникового основания 1, подвижности и диффузионной длины носителей, проводимости созданного в результате записи информации магнитного поля. Как показали результаты эксперимента, соотношение длина-ширина полупроводникового основания 1 составляет от 3:1 до 1:1, а

толщина основания 1, изготовленного из монокристаллического полупроводника, составляет 5-200 мкм; для полученного методом напыления толщина основания снижается до 1 мкм.

В качестве материала подложки 1 используется электронный полупроводник с высокой подвижностью носителей и малым сопротивлением, это германий или кремний с  $\rho_v$ =0,5•2•10<sup>-2</sup> Ом м,  $\mu \simeq 0.3$  м²/(B c), антимония индия с  $\mu \simeq 4.0$  м²/(B c), арсенид индия с  $\mu \simeq 1.5$  м²/(B c).

Элемент памяти работает следующим образом. При подаче сигнала записи на вывод записи 28 открываются транзисторы 3 и 10 и через полупроводниковое основание 1 течет ток  $I_0$   $B_1 \bullet I_c$ , где  $I_c$  ток сигнала записи, а  $B_1$  усредненный коэффициент усиления по току транзисторов 2 и 10. Протекающий через подложку ток  $I_0$  создает в слое ферромагнитного материала 23 магнитное поле, индукция которого

$$B \simeq \frac{\mu_0 \cdot \mu}{4\pi} \frac{I}{r_0} \qquad (1)$$

15

25

30

45

где  $\mu_{o}$ ,  $\mu$  магнитная постоянная и относительная магнитная проницаемость ферромагнитного материала 23,

$r_0$  радиус, проведенный от середины основания 1 до ферромагнитного слоя 23.

После ухода сигнала записи в магнитотвердом слое ферромагнитного материала 23 будет записана информация, представляющая остаточную индукцию В указанного слоя 23. Через полюсные наконечники 24 и 25 из магнитомягкого ферромагнитного материала индукция В воздействует на полупроводниковое основание 1. Эта индукция В действует на полупроводниковое основание 1 независимо от наличия или отсутствия приложенного к выводам 27 и 30 питающего напряжения.

Для считывания записанной информации с элемента памяти необходимо подать на его электроды 27, 30 питающее напряжение, а на вход записи импульс. В результате протекания через полупроводниковое основание 1 импульса тока и действия перпендикулярного току магнитного поля на электродах считывания 26 появится сигнал считывания (ЭДС Холла) в соответствии с зависимостью

$$u_{\mathbf{c}} = R \times \frac{\mathbf{B} \cdot \mathbf{I}}{\mathbf{d}} \qquad (2)$$

где d толщина полупроводникового основания.

Усилительный элемент 31 обеспечивает требуемое усиление сигнала записи ("0", "1") до заданного уровня.

Для стирания информации с целью последующей перезаписи на вывод стирания подается сигнал стирания (например синусоидально-модулированная экспонента), который снимает записанную информацию. В этом случае будут включены в работу транзисторы 2 и 11, а через полупроводниковое основание 1 течет ток в противоположном току записи направлении. Для записи новой информации на вход записи 28 следует вновь подать требуемый сигнал.

Записанную информацию предлагаемый элемент памяти сохраняет после снятия с него питающего напряжения, то есть этот элемент действует, как ППЗУ. Таким же образом предложенный элемент памяти будет функционировать и в матрице ППЗУ.

Создано экспериментально устройство элемент памяти, полупроводниковым основанием которого являлся германий размером 2 х 1 мм и толщиной 200 мкм, в котором методами фотолитографии, диффузии, эпитаксии и напыления были сформированы две триодные пары, усилительный элемент, слой ферромагнитного материала (магнитопровода) с полюсными наконечниками и межслойная изоляция. Заданное значение логических сигналов (1 = 3.8B; "0" = 0.2B) на выходе усилительного элемента формируется сигналом записи напряжения в импульсе 3.5-4.5B.

#### Формула изобретения

Элемент памяти, содержащий ферромагнитный накопитель, транзистор, выводы записи,

#### RU 2075 786 C1

считывания, стирания и вывод питания, отличающийся тем, что элемент выполнен в виде монолитной гибридно-пленочной конструкции, основание которой изготовлено из полупроводникового материала, с торцевых сторон основания послойно размещены пары биполярных транзисторов, а по его длине с обеих сторон последовательно расположены изоляционный слой и слой магнитотвердого ферромагнитного материала, содержащий два полюсных наконечника из магнитомягкого ферромагнитного материала, при этом эмиттеры контактирующих с полупроводниковым основанием внутренних транзисторов соединены с корпусом, базы крайних от полупроводникового основания транзисторов каждой из пар через резистивные слои подключены к базам внутренних транзисторов противоположных пар, коллекторы верхних транзисторных пар соединены с источником питания элемента.